# A Universal Cavity Controller for testing SRF cavities at CERN

D. Barrientos, L. Balocchi, K. Brunner, K. Geis, A. Macpherson, L. Millar, N. Stapley, T. Wlostowski

### **Motivation**

- **Development and validation of SRF Cavities**

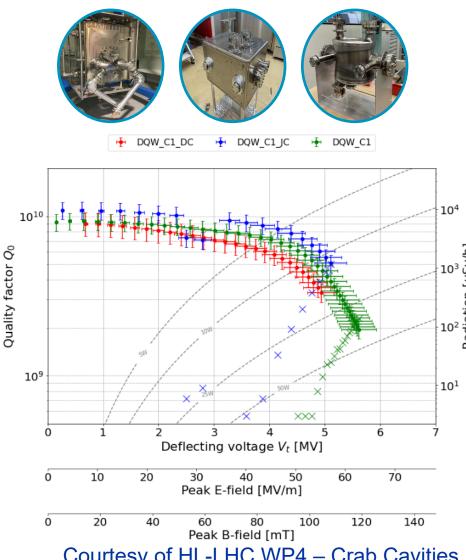

- **Purpose**: Measurement of high quality factor SRF cavities (Q<sub>0</sub> in 10<sup>8</sup> 10<sup>11</sup> range)

- CERN has a variety of cavities with frequencies ranging from 101 -1300 MHz

- LLRF framework must be adaptable to any given cavity type and specific R&D needs

### **Cavity validation**

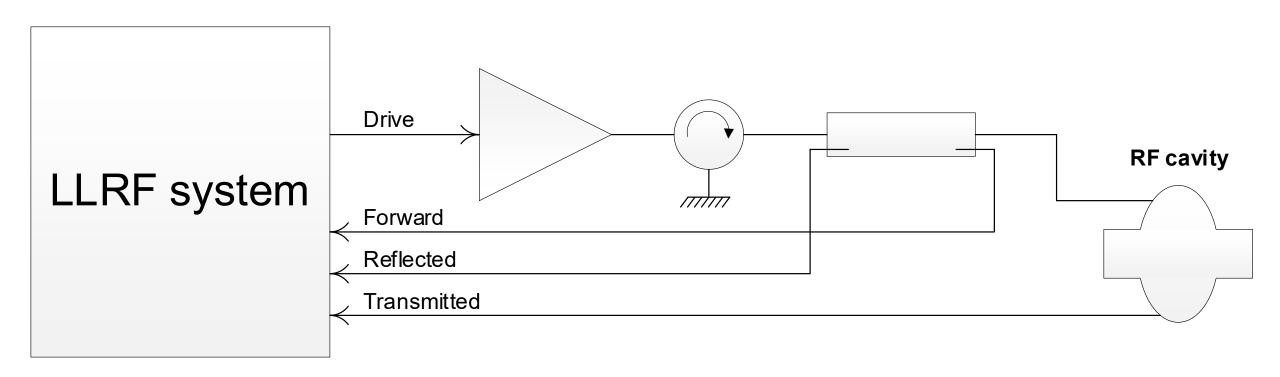

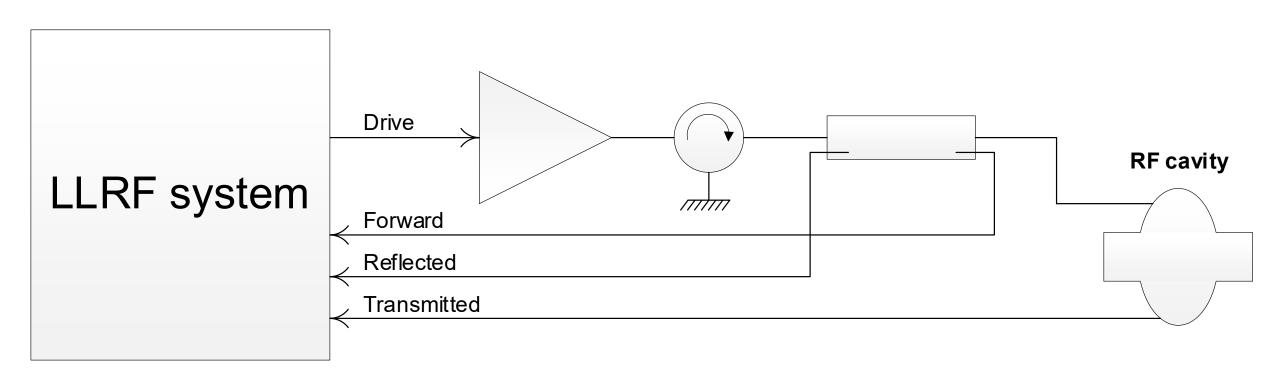

### LLRF example system

### **Cryomodule validation**

Images courtesy of HL-LHC WP4 – Crab Cavities

### **Motivation**

- **Development and validation of SRF Cavities**

- Context: LLRF must follow cavity testing as they progress through their preparation cycle

- RF measurement from bare cavities to beam-ready cryomodules

### **Cavity validation**

14/10/2025

### LLRF example system

### **Cryomodule validation**

Images courtesy of HL-LHC WP4 – Crab Cavities

### **Motivation**

- Development and validation of SRF Cavities

- Requirement: Common architecture to ensure coherence across measurement campaigns

- Measurements include both pulsed and continuous powering operational modes

- Self-Excited Loop and Generator Driven modes required

### **Cavity validation**

### LLRF example system

### **Cryomodule validation**

Images courtesy of HL-LHC WP4 – Crab Cavities

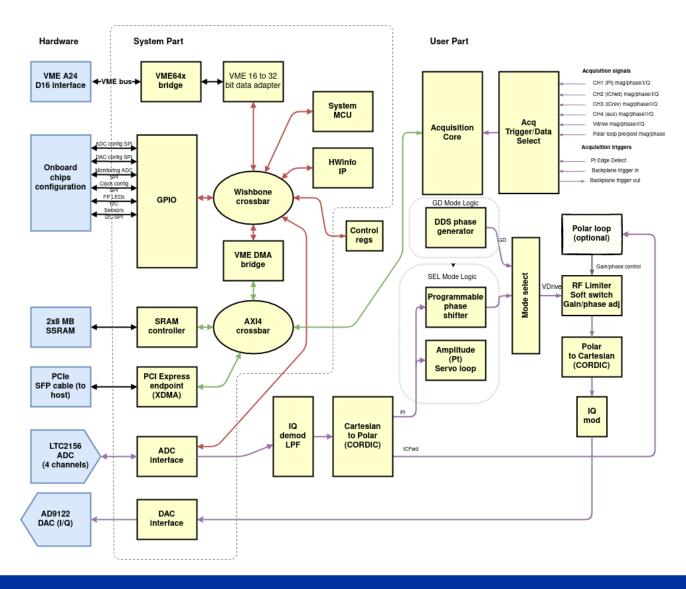

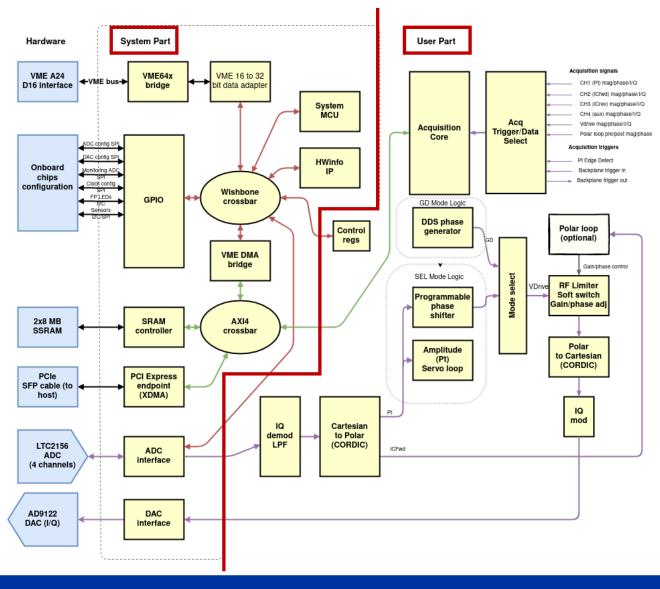

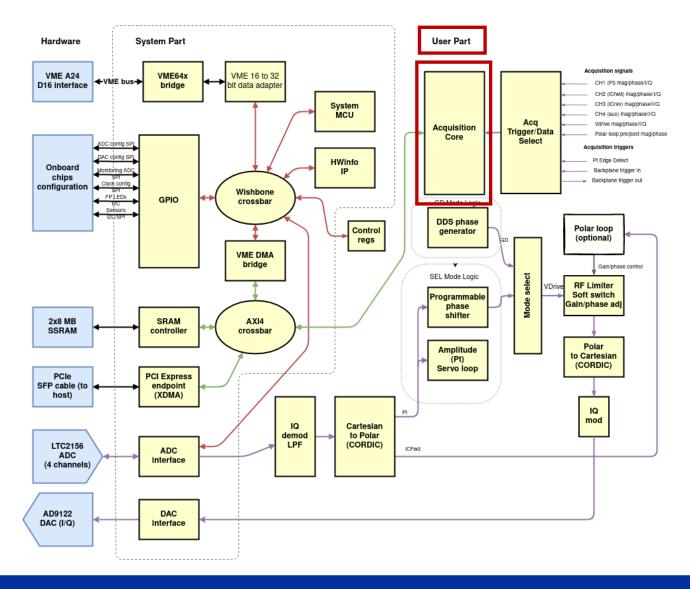

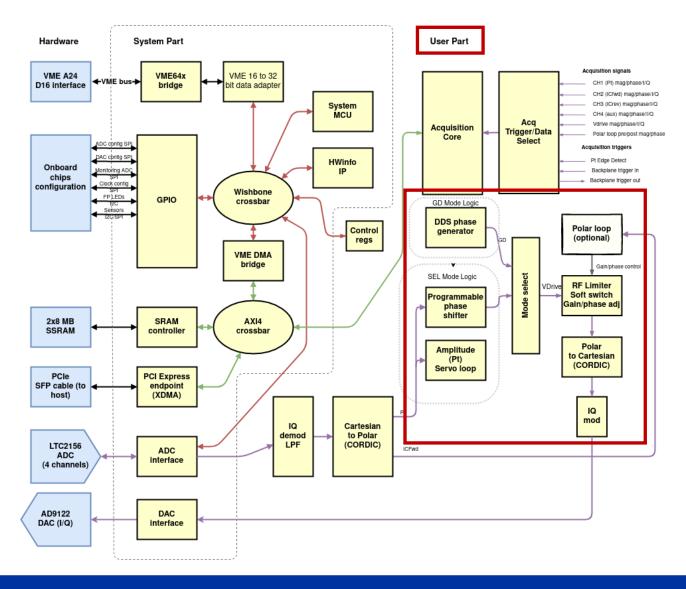

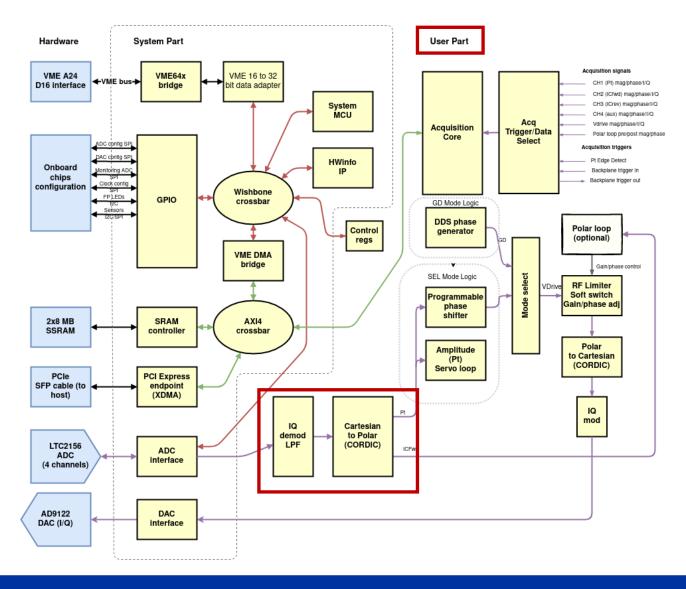

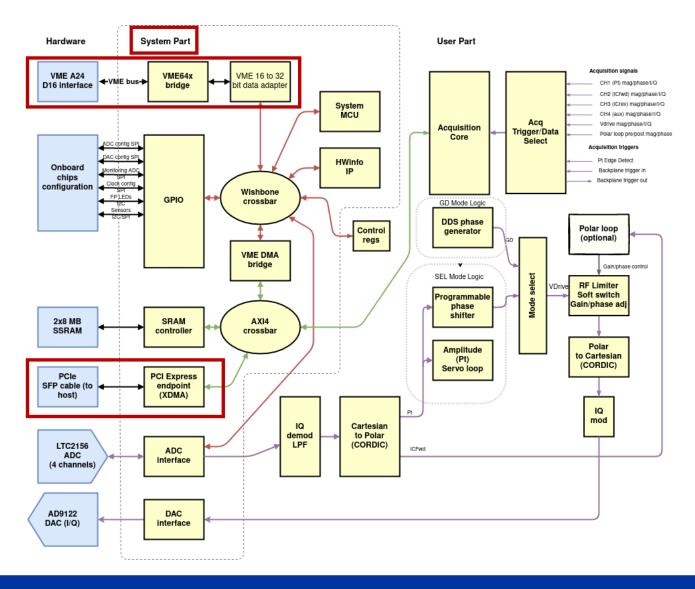

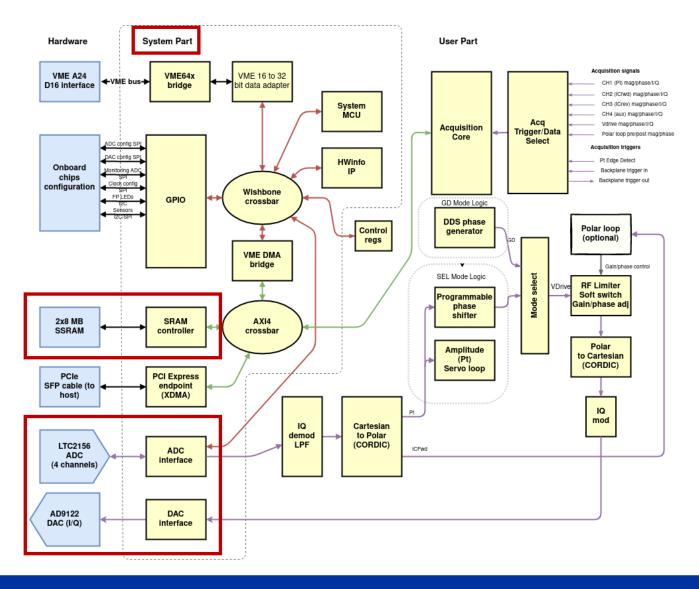

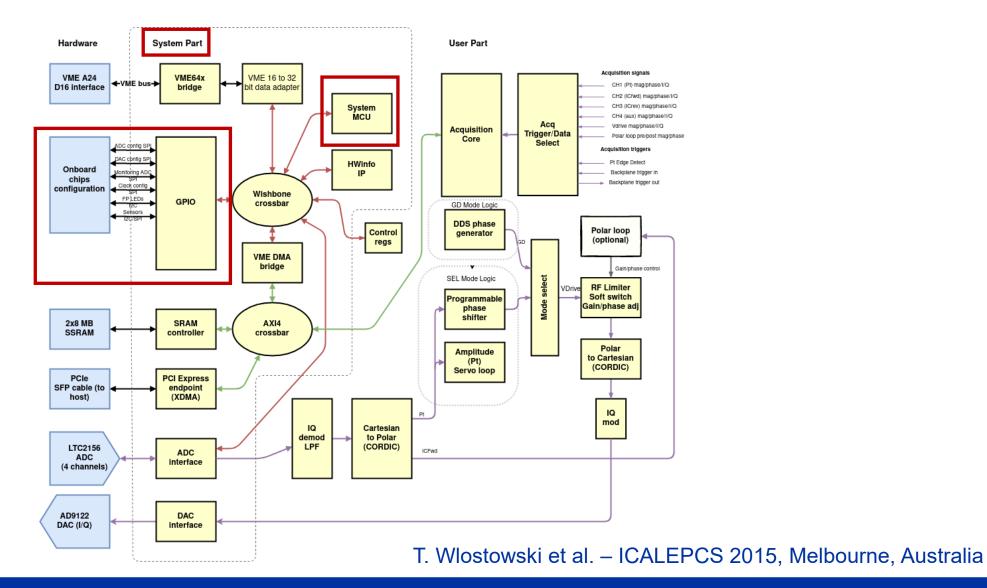

# **System architecture**

# **System architecture**

LLRF cavity controller standardization

# **Hardware**

2x SFPs (up to 2.5 Gbps)— PCI Express

16-bit IQ DAC + Vector modulator (BW = 25 MHz)

4 input channels 14-bit ADCs (BW = 25 MHz)

LO distribution (200 MHz – 1.5 GHz)

-VME A24/D16

16 MB SSRAM

Clock, triggers...

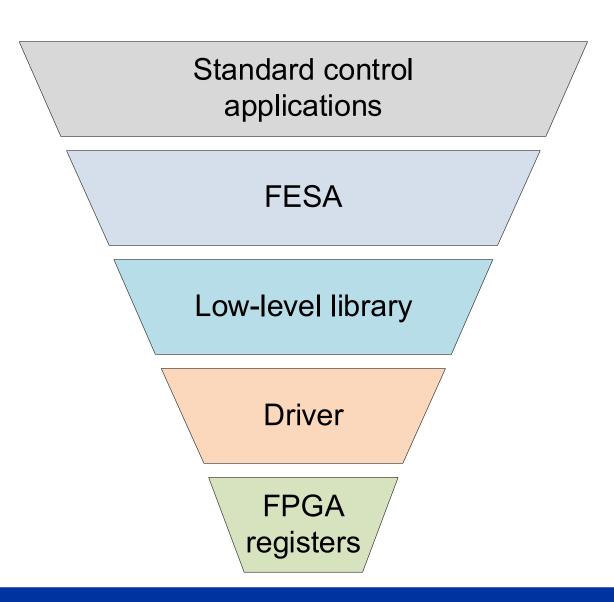

### **Software**

- CERN standard setup

- Reusing control applications layer

- Easy integration into CERN controls system

- Encapsulation of hardware related operations in low-level library

- Code generation for driver and FPGA registers layers

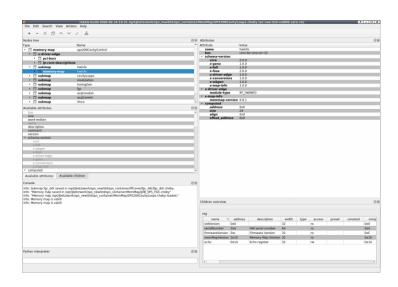

# Reksio (& cheby)

The memory map is the interface The views must be consistent Writing this code is tedious

14/10/2025

- Create memory map with a graphical tool. Verify correctness

- Use code generators for HDL and C++ driver wrapper, FESA class skeleton

- **Quick development/testing using Python**

- **Open-source tools**

T. Gingold, B. Bielawski - FPGA Developers' Forum 2025, CERN

- Hardware independent architecture

- Reusability

- Standard blocks and processes

# **Ease development**

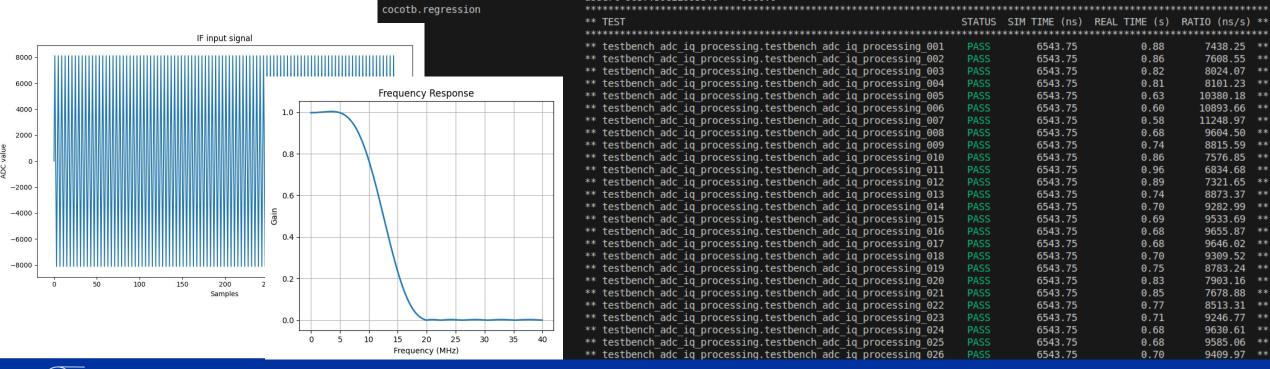

### **Example:**

- Generate IF data with different attenuation, phase offset, frequency.

- Model demodulation, low-pass-filter, CORDIC

- Check magnitude, phase, frequency

- Hardware independent architecture

- Reusability

- Standard blocks and processes

- System/user parts

- MCU

- IP cores + shared libraries

- Continuous Integration

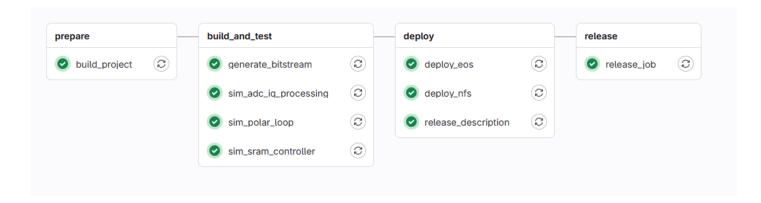

# **Continuous Integration (CI)**

Simulation, implementation, generation

#### CI4FPGA service at CERN

- Scalable VM-based k8s clusters

- Easy-to-use Docker images

- Comprehensive documentation

C. Gentsos - FPGA Developers' Forum 2025, CERN

#### List of tools available as images

The following tools are available in the registry.cern.ch/ci4fpga project:

#### **Toolchains**

- Xilinx Vivado

- Xilinx ISE

- · Microsemi Libero

- Intel Quartus

- Lattice Diamond

#### Simulators

- Riviera-PRO

- GHDL (GCC backend)

- GHDL (mcode backend)

- NVC

- QuestaSim

- ModelSim

- Icarus Verilog

- Altair DSim

#### Lint (and lin-related) tools

- VHDL Style Guide

- Aldec ALINT-PRO

- Verible

#### Documentation generation

- AMIQ EDA DVT

- Doxygen

#### Assorted tools

- YosysHQ OSS CAD Suite

- PetaLinux

- VisualElite

- Synopsys Synplify

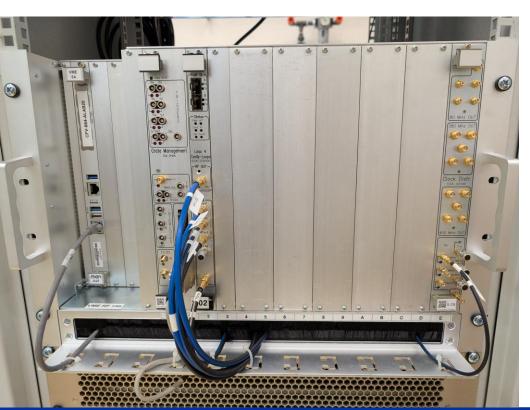

# **Cavity tests**

- Tests setup installation

- Gradual deployment into all SRF test systems

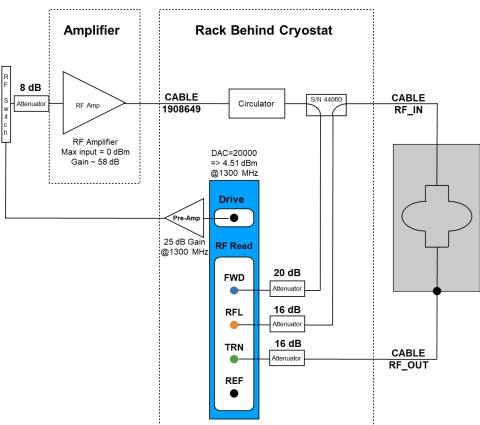

# **Cavity tests**

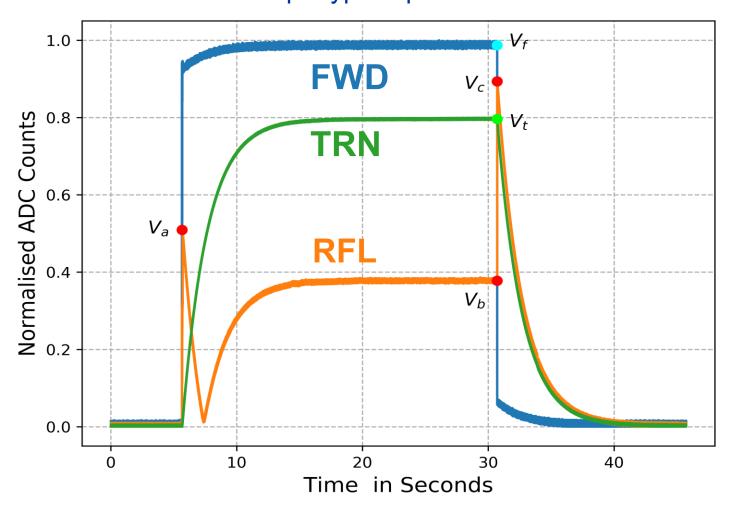

### Self-Excited Loop: Typical pulse measurement

### Recent 400 MHz Crab cavity performance validation campaign

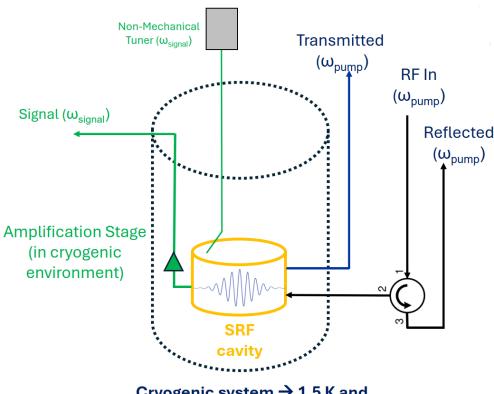

# Future challenges: Axion detection

### Heterodyne approach:

- Drive a high-Q cavity at a frequency, ω<sub>pump</sub>.

- Axion interacts with cavity field and transfers energy to a second mode at  $\omega_{\text{signal}}$ .

- Monitor  $\omega_{sig}$ , the axion mass is given by the frequency difference ( $\Delta\omega = \omega_{pump} \omega_{signal}$ ).

- Mass range can be scanned by varying  $\Delta\omega \rightarrow$  tuning system.

- Initial tests in Q1 2026

### No external B-field required.

Cryogenic system → 1.5 K and 800 mK operation.

L. Millar et al. – 22<sup>nd</sup> International Conference on RF Superconductivity (SRF2025), Tokyo, Japan