## Obvious and Non–Obvious Aspects of Digital Self–Excited–Loops for SRF Cavity Control

## **Abstract**

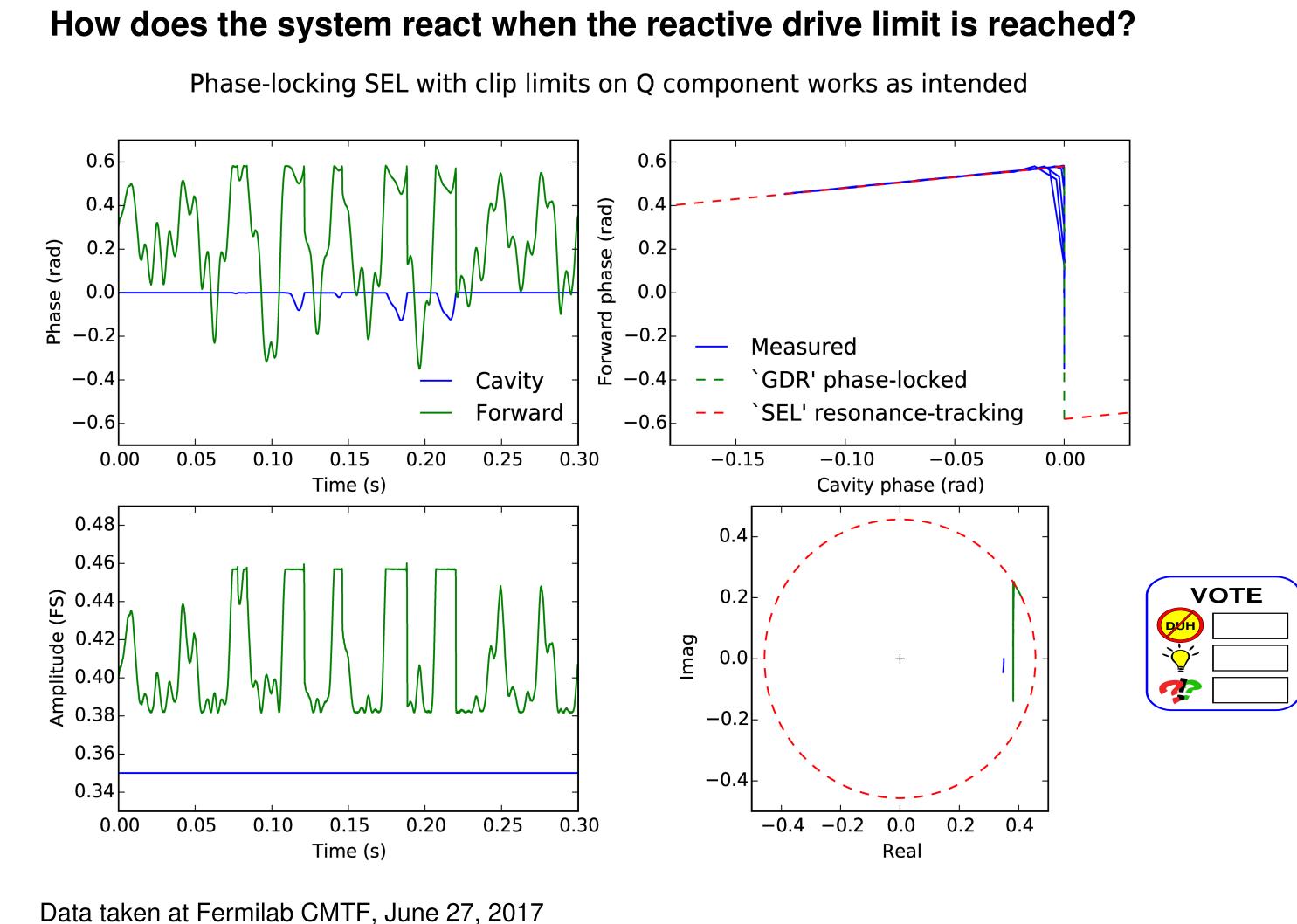

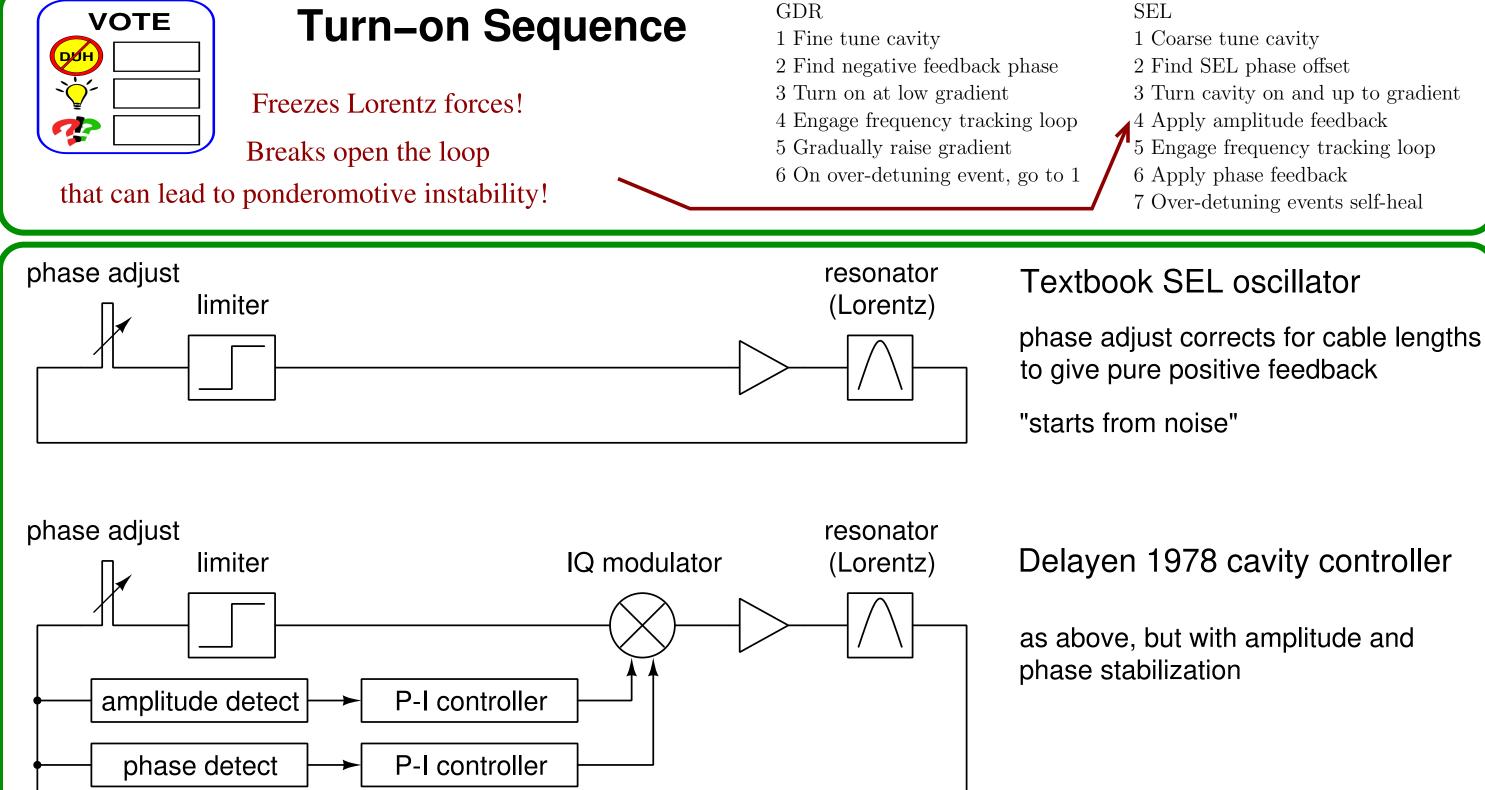

In 1978, Delayen showed how Self-Excited Loops (SEL) can be used to great advantage for controlling narrow-band SRF cavities. Its key capability is establishing closed-loop amplitude control early in the setup process, stabilizing Lorentz forces to allow cavity tuning and phase loop setup in a stable environment.

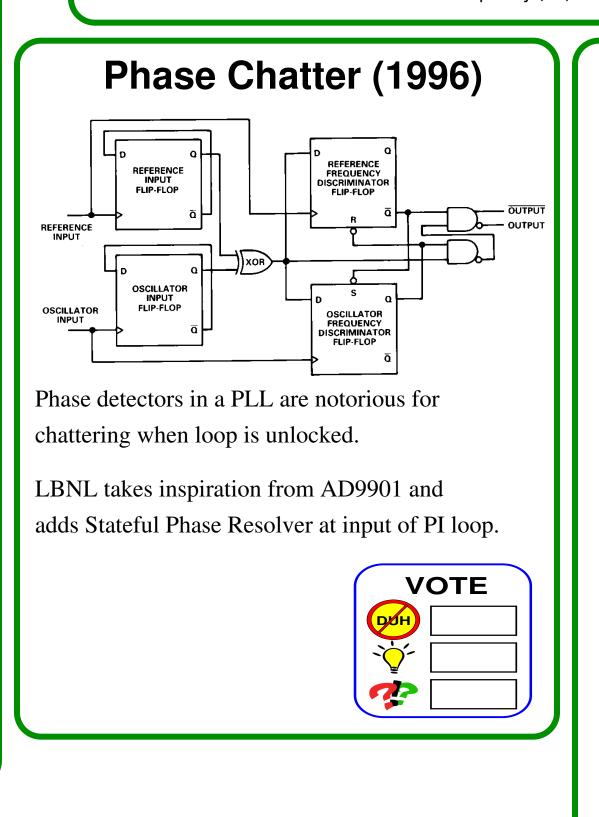

As people around the world implement this basic idea with modern FPGA DSP technology, multiple variations and operational scenarios creep in that have both obvious and non-obvious ramifications for latency, feedback stability, and resiliency.

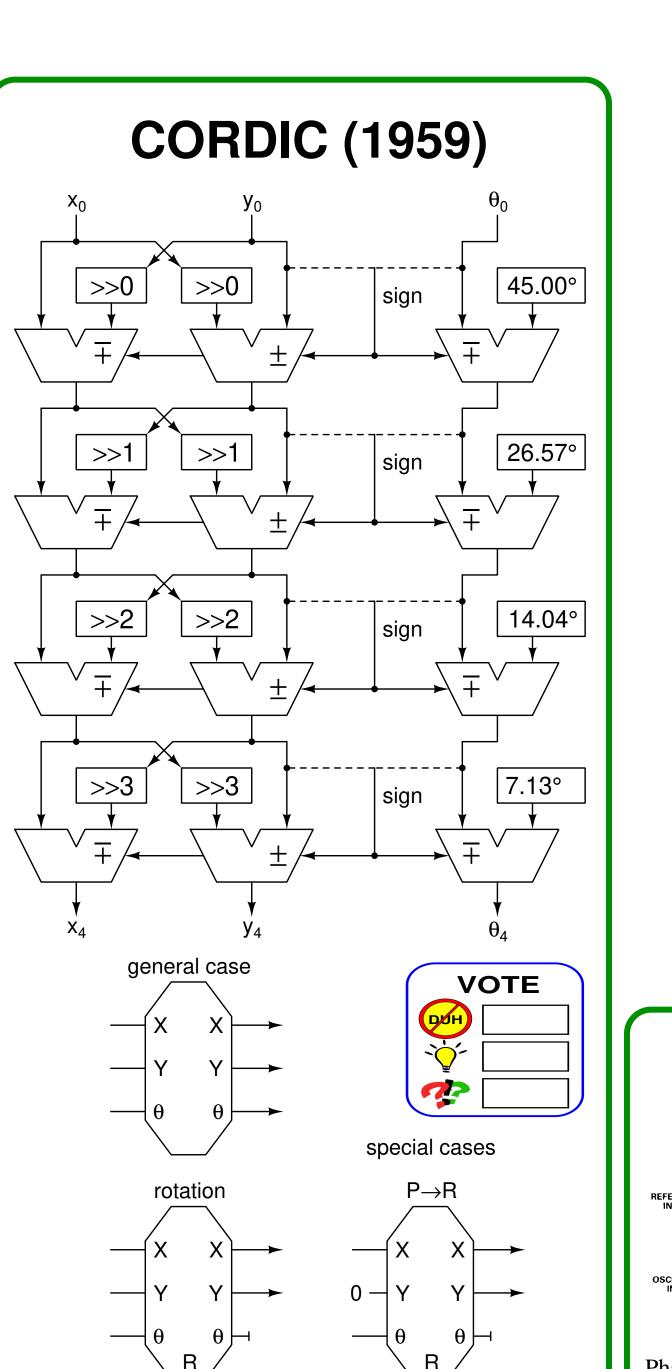

This paper will review the key properties of a Delayen-style SEL when set up for open-loop, amplitude stabilized, and phase-stabilized modes. Then the original analog circuit will be compared and contrasted with the known variations of digital CORDIC-based implementations.

L. Doolittle, S. D. Murthy, LBNL

M. Guran, S. Raman, L. Reyes, P. Varghese, FNAL

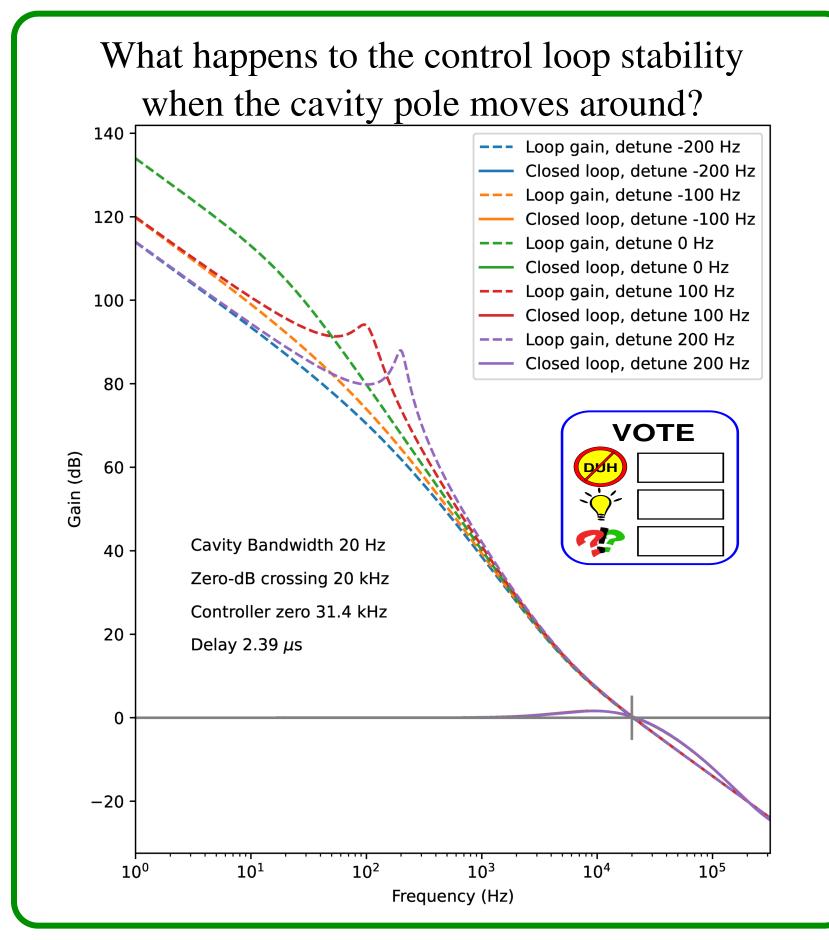

## **Cavity State Space Equation**

$\frac{dV}{dt} = aV + bK + cI$

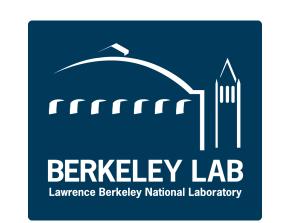

Would be LTI if a, b, and c were constant. But in SRF, the imaginary part of a (detuning) varies with time! Not LTI! For frozen V and ignoring cI, the correct drive is

$$K = K_0 \left( 1 + j \frac{\Im(a)}{\Re(a)} \right)$$

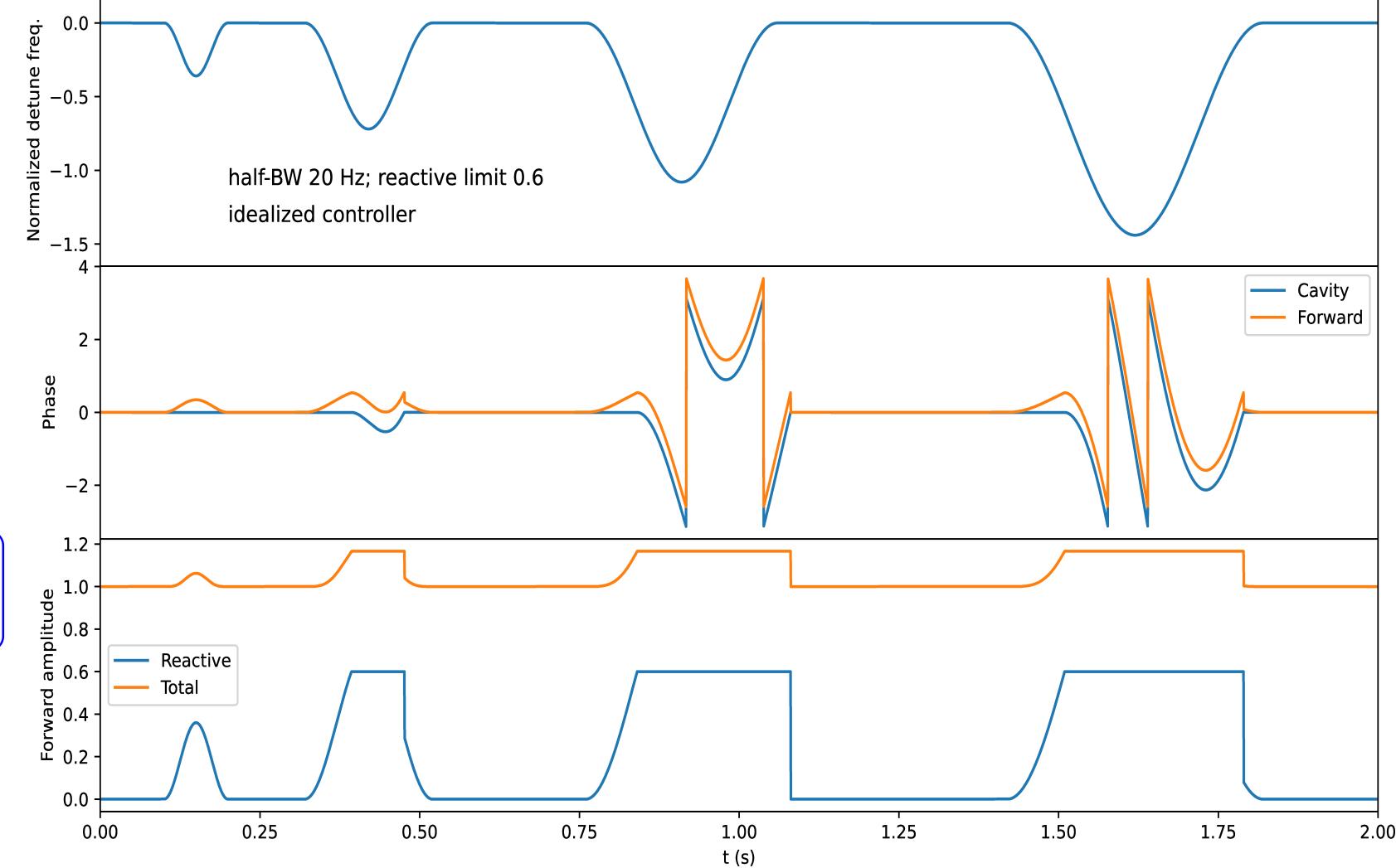

Controller's main job is to stabilize cavity phase by adjusting reactive drive.

**LBNL 2014 JLab 2008** Suggested CORDIC CORDIC CORDIC CORDIC Complex Complex **CORDIC** phase set phase set phase offset phase offset phase offset = PI controller **DALINAC 2011 BARC 2014** phase set dedicated Loop amplitude ADC phase shift amp det **GDR** CORDIC CORDIC Complex Complex amp set multiply Reference phase shift phase set P term only Complex Imag set I term routed to tuner loop

How have people adapted the core idea into the modern FPGA paradigm?

All the same, but all different! Code reuse would be ideal.

Could 'we' at least learn how to mix—and—match implementations and test benches?

$R \rightarrow P$

vectoring

CORDIC blocks in an FPGA are "big". Designs from

JLab and LBNL, at least, time-slice multiple CORDIC

tasks onto a single CORDIC hardware instance.