Thursday, January 16, 2025

# **Streaming Readout PET**

LDRD Q1 Report – January 21, 2025

Cameron Clarke, BRIC Staff Scientist Radiation Detector & Imaging (RD&I) Group

Biomedical Research & Innovation Center

# Q1 ACCOMPLISHED GOALS

#### A) Detector prototype development

- Debug TCP firmware, switch to 10 Gig stack

- Implement off-ASIC ADC firmware

- Design concept for v2.0 front end layout

- B) SRO data processing system development

- Explore SRO analysis architecture options

- Begin ERSAP-based software development

- C) Broader scope project work

- Invention disclosure, APS abstract

- Networking at IEEE meeting

- Planning FY26 UMAB site visit

- Parts ordering ASICs and Network Switch

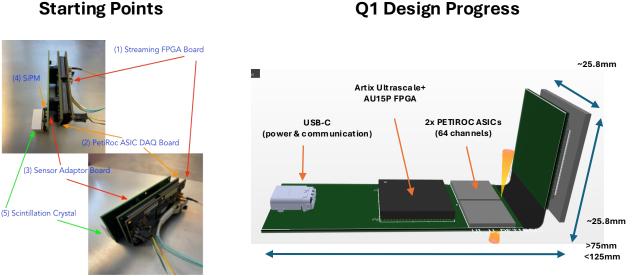

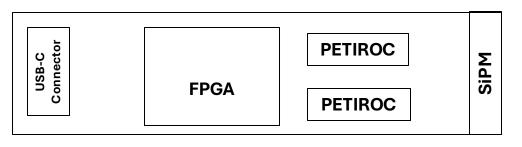

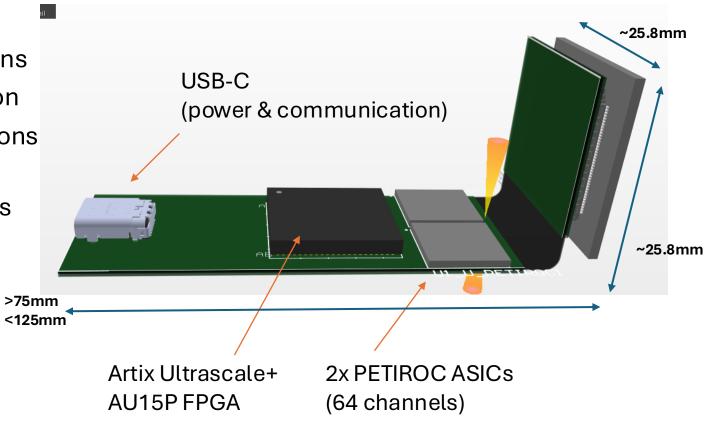

Potential Detector Front-end Electronics v2.0

Existing Detector Front-end Electronics v1.0

Existing KMax GUI running SRO data processing

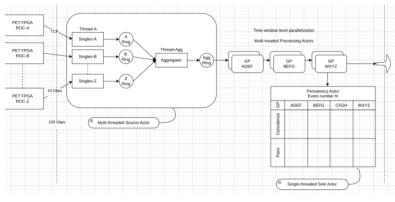

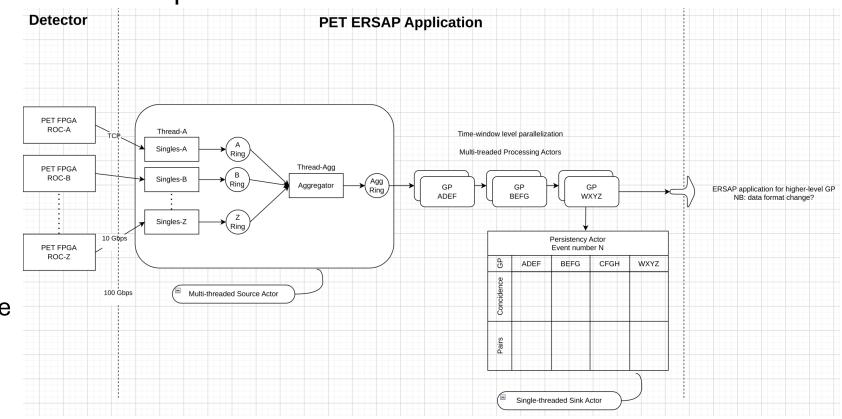

Potential Time-window interleaving ERSAP Architecture

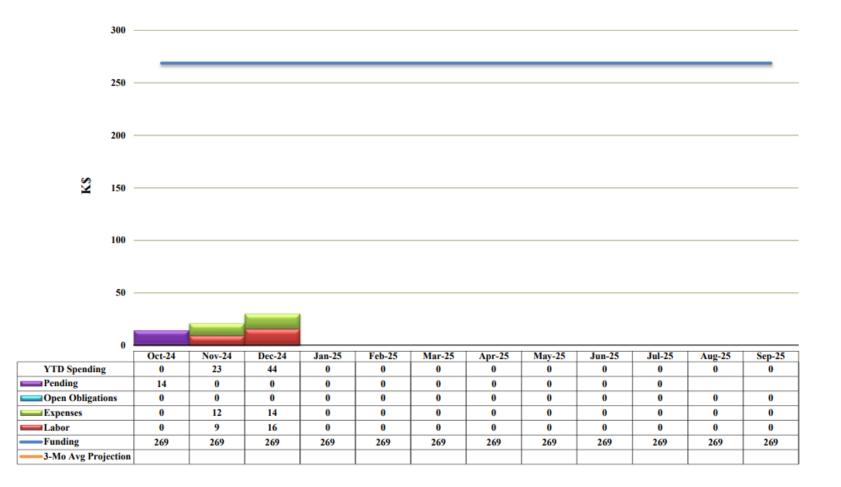

# Spending

#### • Spending is generally on target – <u>slower start-up than scheduled due to delayed start and holidays</u>

- 1) Labor: Spent ~\$10k on labor direct, \$16k loaded

- 2) Equipment: Spent ~\$12k on ASICs for detector front end, ~\$11k pending for network switch

- 3) Travel: <u>Pending</u> ~\$4k for APS meeting travel in March

### BACKUPS

## DELIVERABLES

Deliverables – milestones and timeline:

- Three primary aims

- 1) Implement ERSAP to existing SRO PET detectors, DAQ, and analysis system in FY 25

- 2) Design and build improved version of modular PETIROC ASIC PET detectors in FY 25

- 3) Deploy detector array, perform imaging and parallelized scaling tests with distributed computing in FY 26

| Year 1 |                                                                                                                                                                                                                                                                                                                                                    |                                                               |                                                                                          | Year 2                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| 1)     | Implement ERSAP in FY 25:         (✓) Implement FPGA based PETIROC signal digitization         Factorize analysis components into ERSAP microservices         Reproduce old system performance with ERSAP-based system         Develop vertical multi-threaded, horizontal multi-node scaling                                                      | FY 2025:<br>• Month 3<br>• Month 6<br>• Month 9<br>• Month 12 | nth 3<br>nth 6<br>nth 9<br>nth 12<br><b>3)</b><br><b>025:</b><br>nth 3<br>nth 3<br>nth 6 | <ul> <li>Deploy detector array, imaging and parallelized scaling tests in FY 26:</li> <li>Procure and test new detector front-ends</li> <li>Integrate modular 8-detector array with new SRO system</li> <li>Verify detector and imaging performance for new system</li> <li>Deploy the system and perform phantom imaging tests at UMAB</li> <li>Finalize reports on local and farm streaming scalability tests</li> </ul> | FY 2026:<br>• Month 3<br>• Month 3<br>• Month 6<br>• Month 6<br>• Month 12 |  |

| 2)     | <ul> <li>Design and build modular PETIROC ASIC PET detectors in FY 25:</li> <li>(✓) Optimize FPGA multi-detector readout firmware</li> <li>(✓) Optimize detector power supply and readout cabling</li> <li>Design and order new PETIROC modular detector PCBs</li> <li>Get electronics parts, build, and test 8 new detector front-ends</li> </ul> | FY 2025:<br>• Month 3<br>• Month 3<br>• Month 6<br>• Month 12 |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |  |

# DETECTOR PROTOTYPE DEVELOPMENT

- Debugged existing prototype FPGA firmware

- Issue with missing TCP packets/bad ethernet cable removed bad cable

- Implemented 10-Gig firmware wrapping around existing 1-Gig hardware

- Implemented off-ASIC ADC firmware

- Implemented FPGA firmware to bypass PETIROC digitization, using faster on-board ADC now

- Designed concept for v2.0 front end layout

- Modular detector design locks in design choices for v2.0

# DETECTOR PROTOTYPE DEVELOPMENT

- Designed concept for v2.0 front end layout

- Modular detector design

- Aiming for 4-side buttable

- SiPM and scintillator separated

- Flex cable permits multiple orientations

- & permits thermal and optical isolation

- USB-C connector simplifies connections

- Communication board (not shown) synchronizes and powers all detectors

# SRO PLATFORM DEVELOPMENT

- Explored SRO analysis architecture options

- Event-based processing from FPGA

- Time-windowing at singles or geometry processor

- Potential for timewindowing in the FPGA

- Updated diagram for one potential architecture

- All time-interleaving in a single actor option

- Began ERSAP-based software development

- John is working on GitLab CD/CI implementation

- John is converting KMax singles and geometry processors into ERSAP actors

# BROADER PROJECT GOALS

- Submitted Invention Disclosure, APS Abstract

- Submitted invention disclosure to RTPO

- Poster session abstract at 2025 APS Global Summit

- Networked at IEEE meeting

- Met Simon Cherry at UC Davis

- Met LBNL PET detector researchers

- Attended Edge Computing workshop and contributed to workshop report

- Planned FY26 UMAB site visit

- Discussed planning for trip to UMAB School of Medicine with Mark Smith and Guang Li

- Parts ordered

- Purchased ASICs for 8+1 detectors

- Purchased network switch

# SUMMARY

- We are on track to meeting deliverable goals

- SRO platform development is underway

- Detector front-end design work is underway

- Sub-contracted imaging studies are on track for FY26