## FY25Q1 Project Status

| ID  | Task                                                                                           | status   | Comments                                                  |

|-----|------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------|

| M15 | Establish general framework for RTDP simulation                                                |          | Significant work started on this, but not fully completed |

| M16 | Create configurable CPU proxy component                                                        | <b>√</b> | Fully configurable via command line                       |

| M17 | Create configurable GPU proxy component (hardware and software)                                | ×        | Development to be informed by CPU component               |

| M18 | Create configurable FPGA proxy component (hardware and software)                               | ×        | Development to be informed by CPU component               |

| M19 | Create functioning hardware GPU component (e.g., CLAS12 L3)                                    |          |                                                           |

| M20 | Create functioning hardware FPGA component (e.g., ML4FPGA)                                     |          |                                                           |

| M21 | Configure simulation of full SRO system using existing JLab hardware resources                 |          |                                                           |

| M22 | Establish working test of system that transfers >=100Gbps from CH to compute center            |          |                                                           |

| M23 | Establish working test of system that includes GPU component for portion of the stream         |          |                                                           |

| M24 | Establish working test of system that includes FPGA component for portion of the stream        |          |                                                           |

| M25 | Test system with remote compute facility (e.g., BNL or NERSC) at limits of available resources |          |                                                           |

| M26 | Configure system that results in stream(s) being received by JLab from external source         |          |                                                           |

| M27 | Collaborate with HPDF group to evaluate processing SRO data at JLab for external experiments   |          |                                                           |

| M28 | Complete documentation for platform to be used by non-experts                                  |          |                                                           |

### **Major Highlights**

#### **Cylc-Based Workflows Development:**

Developed and successfully deployed Cylc workflows for: iperf3 testing

Prometheus monitoring

#### **CPU Emulator Development and Testing:**

- **Containerization**: Converted the CPU emulator into an Apptainer-compatible container for portability across HPC environments.

- SLURM Testing

- Configuration Refinement

#### **Configuration Management:**

- Validated standalone configurations

#### **Workflow Automation Progress:**

- **Designed Cylc workflows** for Prometheus and iperf3, with dependency handling for sequential and parallel task execution.

- **Prepared groundwork** for integrating the CPU emulator into the Cylc framework.

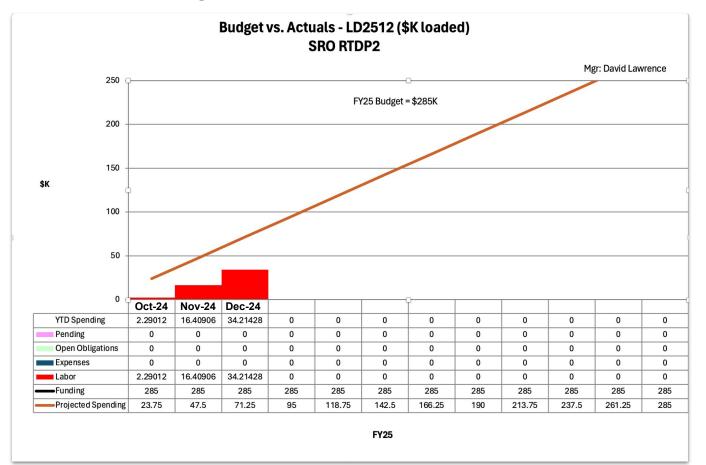

# **Budget**

Personnel shifted to some other pressing projects during FY25Q1.

Time pressure on those has now relaxed and we are refocusing on RTDP in FY25Q2.