### **EIC UG Meeting Early Career Workshop**

### Time measurements using ultra fast silicon detectors with a 120 GeV Proton Beam for the TOPSiDE Detector Concept at The Electron-Ion Collider

MANOJ JADHAV Argonne National Laboratory

July 29, 2021

#### Precision Timing Measurements with UFSDs **EIC UG Meeting Early Career Workshop**

# Outline

- Experimental Involvement

- ► UFSDs for EIC

- ► Low Gain Avalanche Detectors (LGADs)

- ► LGAD to AC-LGAD

- ► Summary

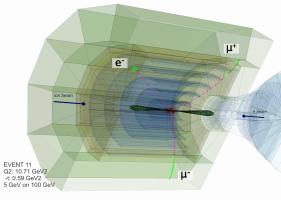

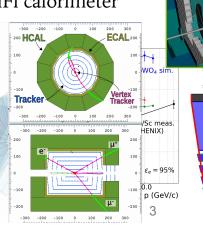

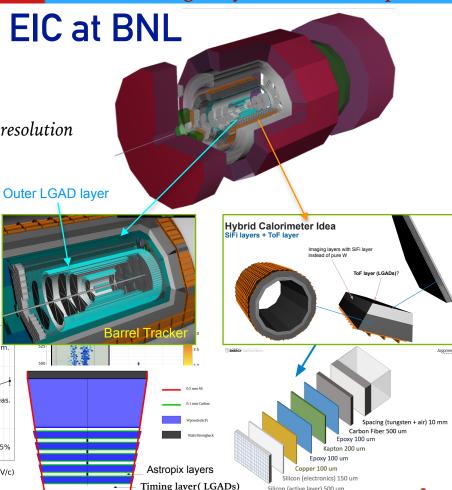

The Electron-Ion Collider (EIC) at BNL EIC UG Meeting Early Career Workshop

## **Experimental Involvement - EIC at BNL**

- The TOPSiDE detector concept at the EIC \*

- UFSDs for Particle Identification using ToF

- \*  $\pi$  K p separation up to 7 GeV/c 10 ps time resolution

- **ATHENA** experiment

- Barrel Silicon Tracker LGAD under study

- **Barrel ECAL**

- Barrel SiW imaging calorimeter

- Barrel hybrid SiW + WSciFi calorimeter

Silicon (active layer) 500 um

Argonne 🕰

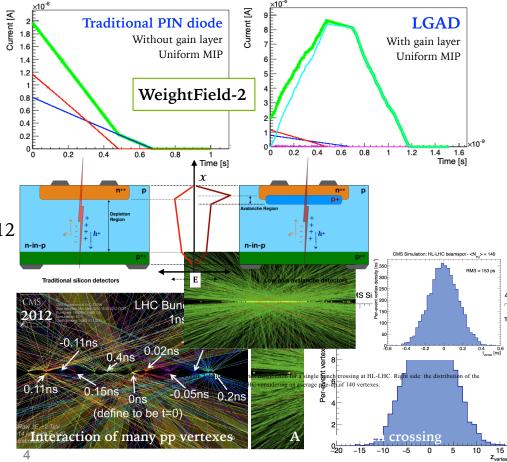

# Introduction to UFSDs

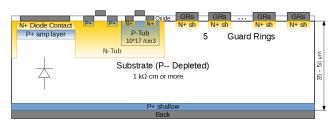

- Low-Gain Avalanche Diode (LGAD)

- \* Gain layer (n<sup>++</sup>- p<sup>+</sup> p p<sup>++</sup>)

- High E-field in gain region

- Multiplication process

- Internal gain of 10-70

- \* High signal-to-noise (SNR) ratio

- One bunch crossing with ~50 overlapping events recorded by the CMS experiment in 2012

- At HL-LHC it will be at the order of 150–200 events per bunch crossing

- The time-dimension improves reconstruction process by considering only time-compatible hits in the pattern recognition phase

- Particle Identification using Time-Of-Flight method

LGADs are considered potential candidate at the EIC

Figure 1 Interaction time of many proton-proton vertexes happening in the same bunch crossing in the case of  $\sim$  50 overlapping events. The vertexes are spaced 10's of pico seconds apart.

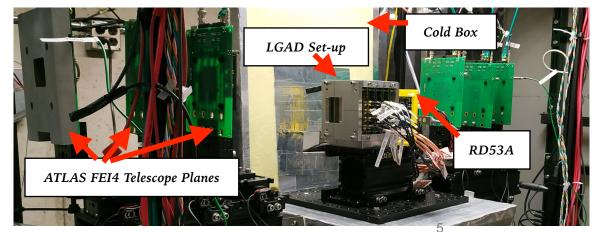

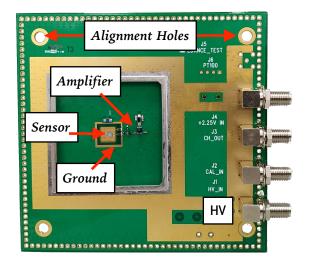

# LGAD Measurement Setup

- \* Single channel readout board

- Wide bandwidth 2 GHz and gain 10

- \* Total trans-impedance of  $4700\Omega$

- followed by commercial amplifier

- 120 GeV Proton Beam at Fermilab

- \* Data were collected in spills of 4 sec

- Trigger rate between 1 and 5 Hz

200

300

400

500

$\Delta t_{cfd50}$

100

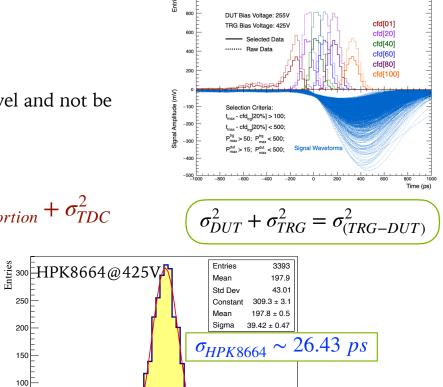

## Analysis methods

### Analysis to mimic timing readout system

- Constant Fraction Discriminator (CFD) method

- Signal amplitude should be above 5 times of noise level and not be saturated by scope or readout chain

- The RMS of time difference between DUT and TRG

∰ 700 HPK1.2@250V

600

500

400

300

200

100F

-400

-300

-200

-100

$$\sigma_t^2 = \sigma_{TimeWalk}^2 + \sigma_{Jitter}^2 + \sigma_{LandauNoise}^2 + \sigma_{Distortion}^2 + \sigma_{TDC}^2$$

Entries

Mean

Mean

Sigma

100

0

Std Dev

Constant

200

8116

-28.47

54.53

$\sigma_{HPK1.2} \sim 29.25 \ ps$

250

200

150

100

50

-200

-100

0

716.4 ± 8.0

$-24.65 \pm 0.52$

41.36 ± 0.55

300

$\Delta t_{cfd50}$

6

LGAD Results and Summary EIC UG Meeting Early Career Workshop

# **Results and Summary - LGADs**

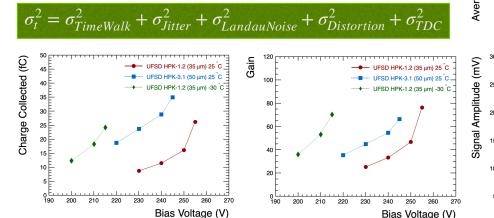

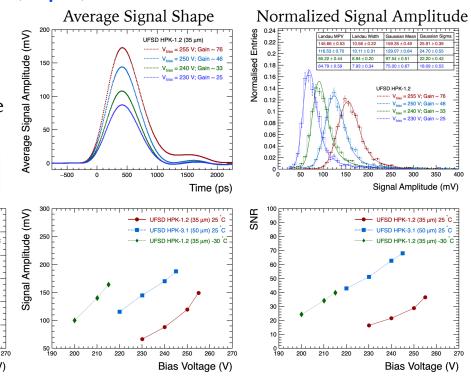

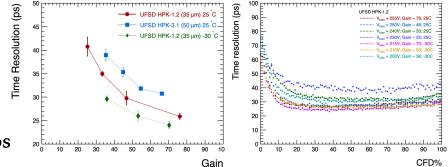

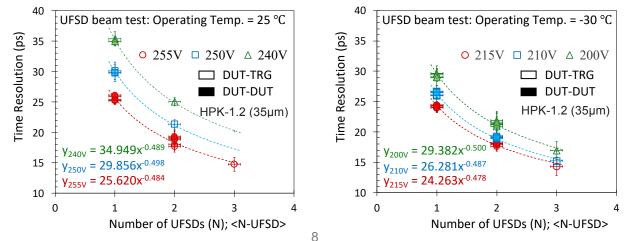

### Test beam results for HPK 1.2 ( $35\mu m$ ), $3.1(50\mu m)$

- Constant Fraction Discriminator (CFD) method

- The RMS of time difference between DUT and TRG gives time resolution

- Charge Multiplication increases with bias voltage increasing the Gain

LGAD Results and Summary EIC UG Meeting Early Career Workshop

# **Results and Summary - LGADs**

- Timing resolution for 3 layers of LGADs

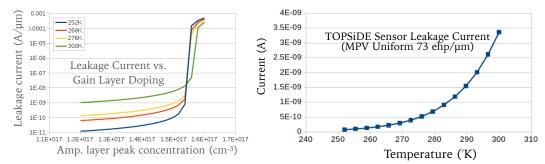

- Timing resolution improves at low temperature but restricted by the lower breakdown voltage

- Very short rise time of ~350-400 ps were obtained

- M. Jadhav et al 2021 <u>JINST 16 P06008</u>, <u>arXiv:2010.02499</u>

- Achieved timing resolution of 14.31 ± 1.52 ps

- Fastest test beam measurements to date

#### LGAD to AC-LGAD EIC UG Meeting Early Career Workshop

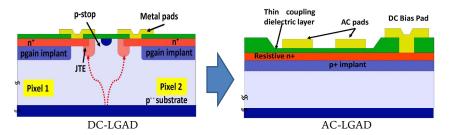

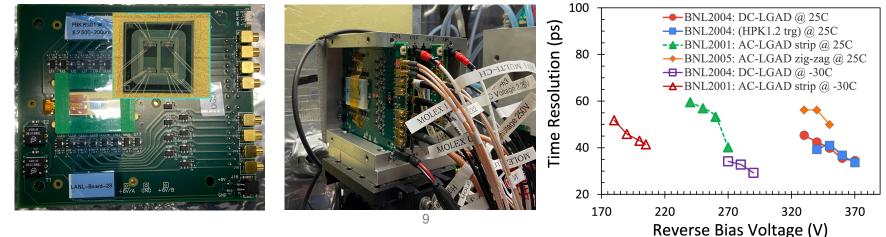

# **AC-LGAD** Testing

### Test beam campaign for AC-LGADs

- Dielectric layer for isolation and AC-coupling

- \* Results in 100% fill factor

- AC-LGADs and Multi-Channel Boards

- Testing at the 120 GeV proton test-beam in collaboration with UCSC and BNL as a part of the EIC LGAD consortium

- \* The LGADs with strip and pixel array geometry are mounted on multi-channel readout boards

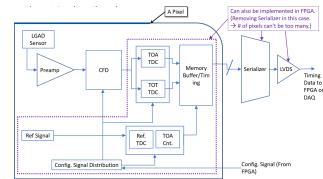

- Upgrading DAQ from software based CFD to multi-channel digitizer

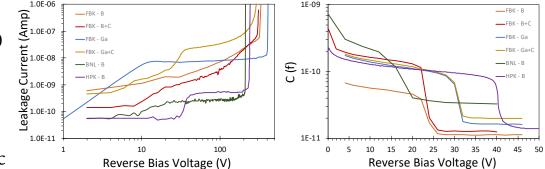

### LGAD Development at Argonne EIC UG Meeting Early Career Workshop

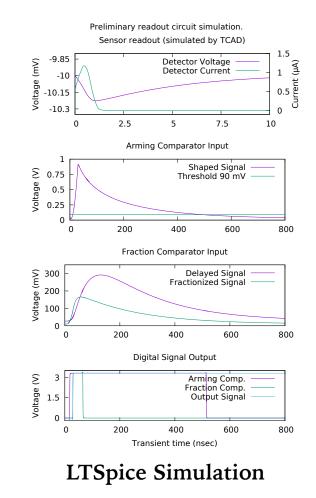

# LGAD Development at Argonne

- TCAD simulation ATLAS Silvaco

- \* Sensor with pad size of  $1 \times 1 \text{ mm}^2$  and thickness 50  $\mu m$

- The goal is to integrate readout electronics using HV-CMOS (PicoPix)

- The first stage includes preamplifiers, shaper, constant fraction discriminator

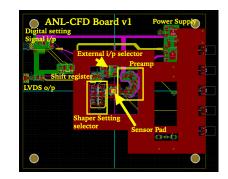

- Being prototyped on PCB board (w/o TDC ) before implementation on to pixel

- \* Time-of-Arrival, Time-over-Threshold

- FPGA Ultra96 programmable for up to 4 channels

## Summary

- \* Characterized and tested LGAD (DC & AC) in the lab as well as test beam

- \* Developed DAQ framework based on PyVISA and Python

- Achieved timing resolution of 14.31 ± 1.52 ps → Fastest test beam measurements to date

- M. Jadhav et al 2021 <u>JINST 16 P06008</u>, <u>arXiv:2010.02499</u>

- \* Testing of AC-LGADs with zig-zag strip structure (targeted for publication)

- Ongoing tasks

- \* Upgrading DAQ from software based CFD to multichannel digitizer

- Providing trigger from LGAD sensor to ATLAS telescope

- \* Testing CFD read-out boards and development of Monolithic LGADs

**Backups** EIC UG Meeting Early Career Workshop

## Back-up Slides

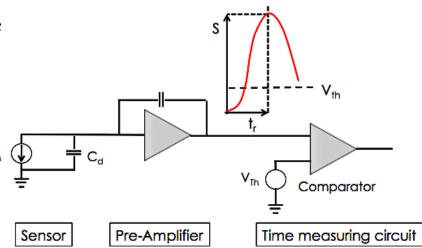

# **Timing Measurements**

Time resolution of the Silicon detector can be expressed as contribution of,

$$\sigma_t^2 = \sigma_{TimeWalk}^2 + \sigma_{Jitter}^2 + \sigma_{LandauNoise}^2 + \sigma_{Distortion}^2 + \sigma_{TDC}^2$$

- Timing capabilities of the silicon detector are characterized by signal at preamplifier output and TDC binning

- Time of arrival is set when signal crosses the comparator threshold

- Timing resolution is measured as RMS of the timing difference (or TOF of a MIP) between the device-under-test (DUT) and the trigger.

A simple time-tagging detector

#### Introduction to UFSDs EIC UG Meeting Early Career Workshop

# **Timing Measurements**

Time Walk: the voltage value V<sub>th</sub> is reached at different times by signals of different amplitude

$$\sigma_{TimeWalk} = \left[\frac{V_{th}}{\mathrm{d}v/\mathrm{d}t}\right]_{\mathrm{RMS}}$$

Constant fraction discriminator (CFD) with TOA defined at % of signal amplitude reduces time-walk contribution

Jitter: variation in time caused by the noise in the system

$\sigma_{Jitter} = \frac{Noise}{\mathrm{d}V/\mathrm{d}t}$

The noise is summed to the signal, causing amplitude variations

The predominant contribution to the timing resolution

#### Introduction to UFSDs EIC UG Meeting Early Career Workshop

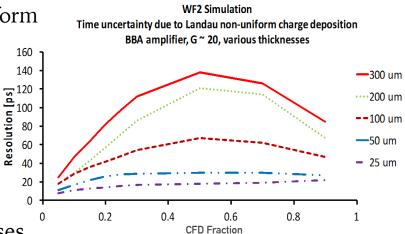

## **Timing Measurements**

- Landau Noise: introduced by a particle's non-uniform charge deposition along its passage

Decreases with thickness of the sensor

Jitter and Landau noise contribute almost equally

- Distortion: The signal distortion is negligible in silicon for the saturated drift velocity and uniform weighting field.

- **TDC:** The TDC effect is minimal in most of the cases

$\sigma_{TDC} = \frac{TDC_{bin}}{\sqrt{12}}$

2021

The time resolution is minimized by maximizing the slew rate dV/dt of the signal and minimizing the noise

Thinner Sensor => faster rise time => larger slew rate

We need large and short signals!

15

#### Introduction to UFSDs EIC UG Meeting Early Career Workshop

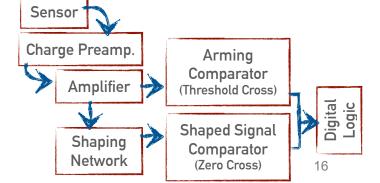

## **Readout Development**

- Front-end readout components

- ➡ Shaper, amplifier, discriminators, digitizers (TDC)

- Time-of-Arrival, Time-over-Threshold

- \* The first stage includes preamplifiers, shaper, constant fraction discriminator

- Being prototyped on PCB board (w/o TDC) before implementation on to pixel

- ➡ FPGA <u>Ultra96</u> programmable for up to 4 channels