# 4π Silicon Hybrid Detector with Charged Particle Identification and Highest Position Resolution for an Experiment at EIC

### Rachid Nouicer, for the 4PISHDEIC Group Brookhaven National Laboratory

SILICON PIXEL-BASED PARTICLE VERTEX AND TRACKING DETECTORS TOWARDS THE US ELECTRON ION COLLIDER WORKSHOP, September 02-04, 2020

a passion for discovery

# **Project Member: International Collaboration**

#### Project members have extensive record on the construction of silicon detectors:

- Silicon strip

- detector

- Silicon pixel

- detector

- Silicon hybrid pixel

- SOIMPXD

- UFSD: LGAD,

AC-LAGD

- Silicon readout

- 0.000

- Silicon assembly

- Cooling system

- Integration

- Commissioning

- And more

**Project Members:**

Whitney Armstrong, Manoj Jadhav, Sylvester Joosten, Jessica Metcalfe, and Zein-Eddine Meziani

Argonne National Laboratory, 9700 S. Cass Avenue, Lemont, IL 60439, United States

Daniel Cacace, Giacomini Gabriele, John Haggerty, David Lynn, Eric Mannel, Gerrit van Nieuwenhuizen, Rachid Nouicer, and Robert Pisani Brookhaven National Laboratory, Upton, NY 11973, United States

Yasuo Arai, Akimasa Ishikawa, Yoichi Ikegami, Ikuo Kurachi, Toshinobu Miyoshi, Manabu Togawaand, and Toru Tsuboyama High Energy Accelerator Research Organization KEK, Tsukuba, Japan

> Miho Yamada Tokyo Metropolitan College of Industrial Technology, Tokyo, Japan

Simone Mazza, Hartmut Sadrozinski, Bruce Schumm, and Abraham Seiden University of California, 1156 High Street Santa Cruz, CA 95064, United States

> Kazuhiko Hara University Tsukuba, Tsukuba, Japan

#### We welcome people/institutions to join the project

**Rachid Nouicer**

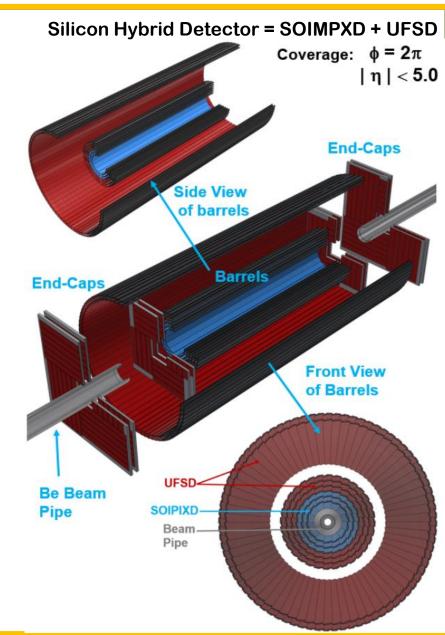

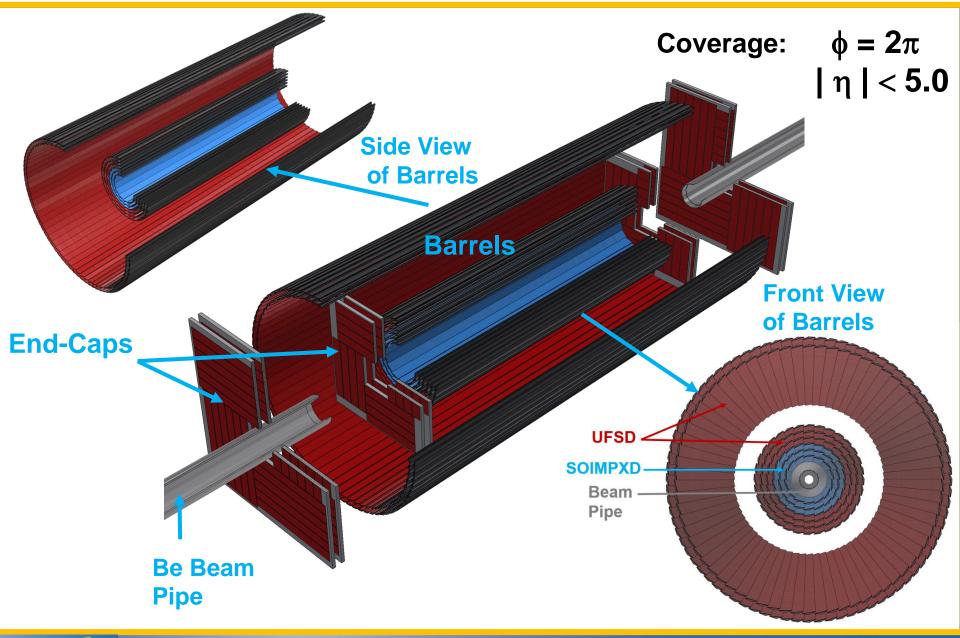

# $4\pi$ Silicon Hybrid Detector = SOIMPXD + UFSD

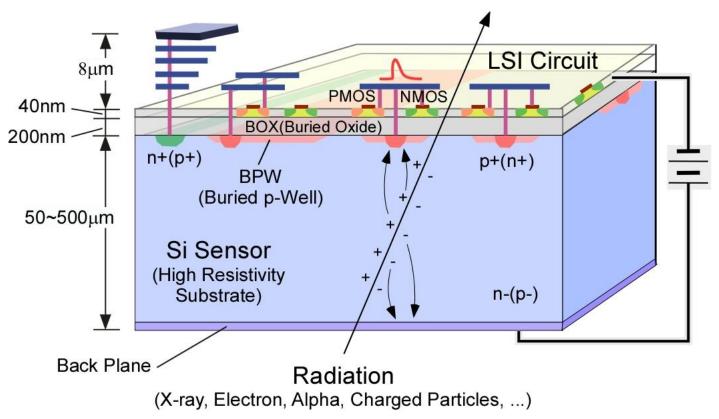

#### Why Silicon-On-Insulator Monolithic PiXel Detector (SOIMPXD)?

- Monolithic device. No mechanical bonding.

- Fabricated with semiconductor process only  $\rightarrow$  High reliability and Low Cost.

- High Resistive fully depleted sensor (50 um~700 um thick) with Low sense node capacitance → Large S/N.

- On Pixel processing with CMOS circuits.

- No Latch up and very low Single Event cross section.

- Can be operated in wide temperature (1K-570K) range.

- Based on Industry Standard Technology

Why Silicon-On-Insulator Monolithic PiXel Detector (SOIMPXD)?

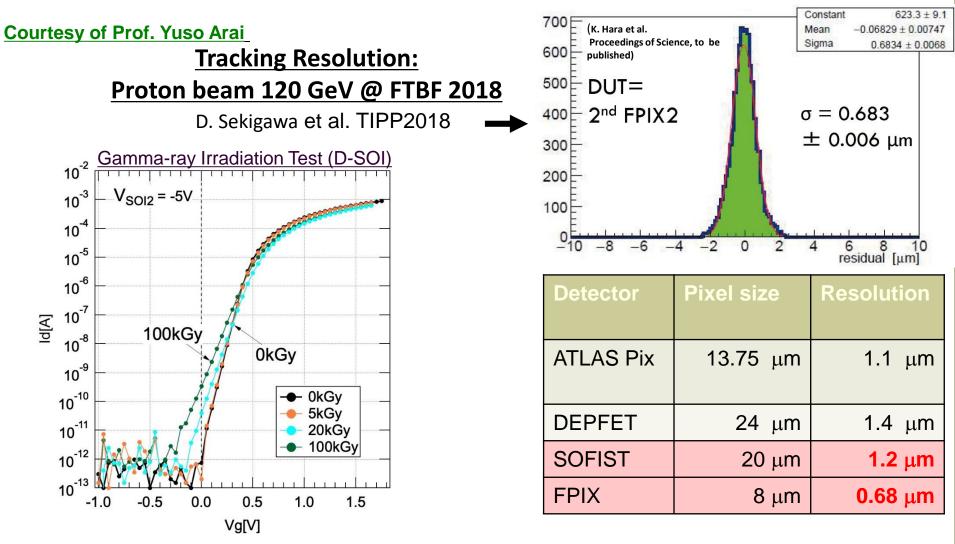

SOIMPXD has the best tracking position resolution in the world 0.68  $\mu$ m, high radiation

tolerance more than 10 Mrad (Si), time resolution ~  $1\mu$ s, and low material budget.

**Rachid Nouicer**

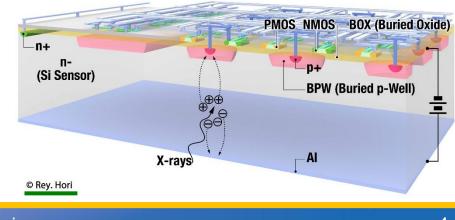

#### Courtesy of Prof. Yuso Arai

Monolithic Detector having fine resolution of silicon process and high functionality of CMOS LSI by using a SOI Pixel Technology.

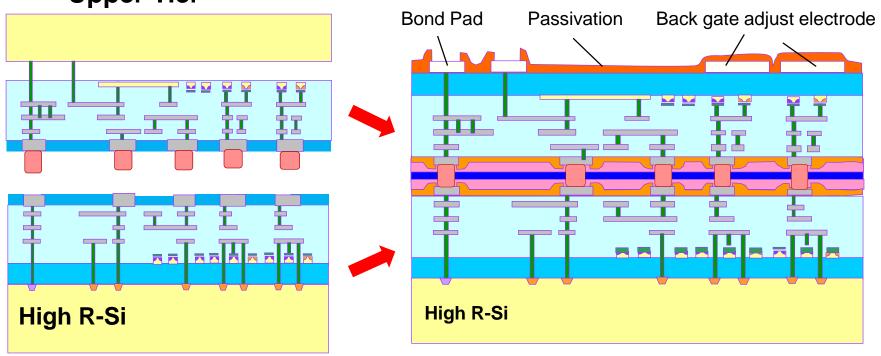

# **3D Vertical Integration**

**Upper Tier**

SOFIST Ver. 4

**Lower Tier**

Upper and Lower Tier chips are produced in a same wafer and bonded chip to chip.

#### Extensive Program Achieved on SOIMPXD using Beam Test at FNAL

|                           | SOFIST1                                                         | SOFIST2                                                                                                                                                | SORST3                                                                                                                                           | SOFIST4 (3D)                                                                                                                                     |

|---------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Courtesy of Mil           | Beam test at FNAL<br>in Jan. 2017<br>Analog signal<br>ho Yamada | Beam test at FNAL<br>in Feb. 2018<br>Analog signal or<br>Timestamp                                                                                     | Beam test at FNAL<br>in Feb. 2019<br>Analog signal and<br>Timestamp                                                                              | Beam test at FNAL<br>in Feb. 2020<br>Analog signal                                                                                               |

| Chip Size (mm²)           | 2.9 × 2.9                                                       | 4.45 × 4.45                                                                                                                                            | 6×6                                                                                                                                              | 4.45 × 4.45                                                                                                                                      |

|                           |                                                                 |                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                                  |

| Pixel Size (µ m²)         | 20 × 20                                                         | 25 × 25                                                                                                                                                | 30 × 30                                                                                                                                          | 20 × 20                                                                                                                                          |

| Pixel Array               | 50 × 50 (Analog Signal)                                         | 64 × 64 (Time Stamp)<br>16 × 64 (Analog Signal)                                                                                                        | 128 × 128<br>(Analog signal and Time stamp)                                                                                                      | 104 × 104<br>(Analog signal and Time stamp)                                                                                                      |

| Functions (Pixel)         | Pre. Amplifier (CSA)<br>Analog signal memory (2 hits)           | Pre. Amplifier (CSA)<br>Comparator (Chopper inverter)<br>Shift register (DFF × 2)<br>Analog signal memory (2 hits)<br>or<br>Time stamp memory (2 hits) | Pre. Amplifier (CSA)<br>Comparator (Chopper inverter)<br>Shift register (DFF × 3)<br>Analog signal memory (3 hits)<br>Time stamp memory (3 hits) | Pre. Amplifier (CSA)<br>Comparator (Chopper inverter)<br>Shift register (DFF × 3)<br>Analog signal memory (3 hits)<br>Time stamp memory (3 hits) |

| Functions (On Chip)       | Column ADC (8 bit)                                              | Column ADC (8 bit)<br>Zero-suppression logic                                                                                                           | Column ADC (8 bit)                                                                                                                               | Column ADC (8 bit)                                                                                                                               |

| Wafer                     | FZ n-type (Single SOI)                                          | Cz p -type (Double SOI)                                                                                                                                | FZ p -type (Double SOI)                                                                                                                          | FZ p -type (Double SOI)                                                                                                                          |

| Wafer Resistivity (kQ-cm) | 2≤                                                              | 1≤                                                                                                                                                     | 3 - 10                                                                                                                                           | 3 - 10                                                                                                                                           |

| Status                    | Delivered (Dec. 2015)<br>Position resolution ~1.4 µm            | Delivered (Jan. 2017)<br>Time resolution ~1.55 µs                                                                                                      | Delivered (May. 2018)<br>Under evaluation                                                                                                        | Delivered (Jan. 2019 ~)                                                                                                                          |

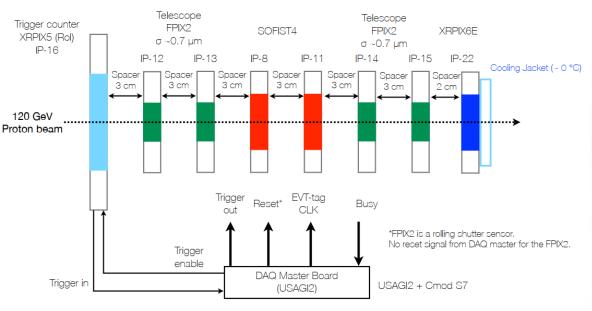

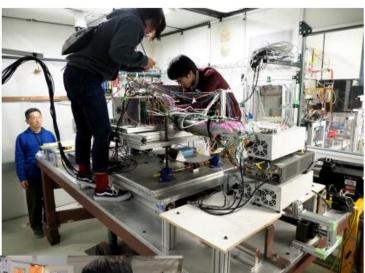

#### SOIMPXD @ FBTF Feb. 26th - Mar 8th, 2020: 120 GeV Proton Beam

#### **Courtesy of Miho Yamada**

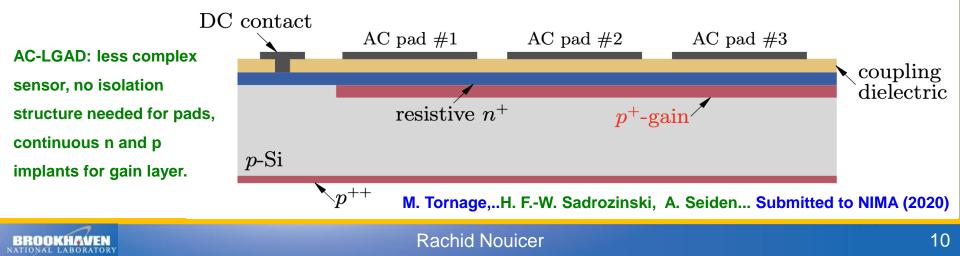

- Ultra Fast Silicon Detector (UFSD) are thin pixelated silicon sensors based on the Low Gain Avalanche Detector (LGAD) design which uses one extra implant during the sensor fabrication to achieve an intense electric field in a few micron region near the detector junction. The large electric field is able to start an avalanche multiplication for the collected electrons. The resulting large and fast signal allows the measurement of the particle hit time determination to be improved from nanoseconds to picoseconds. Developed by CNM Barcelona (Spain) first, HPK Hamamatsu (Japan), FBK Trento (Italy), and BNL (US).

- Can deliver the timing accuracy needed for ToF/PID and physics at the EIC

- > Can be arranged in an array covering large areas as conventional silicon detectors for tracking

- The AC-LGADs are actually fairly simple compared to for example strip detectors (no large number of individual strips with polysilicon resistors) and not exceptionally difficult to fabricate, BNL was able to make them. Should result in reduced cost.

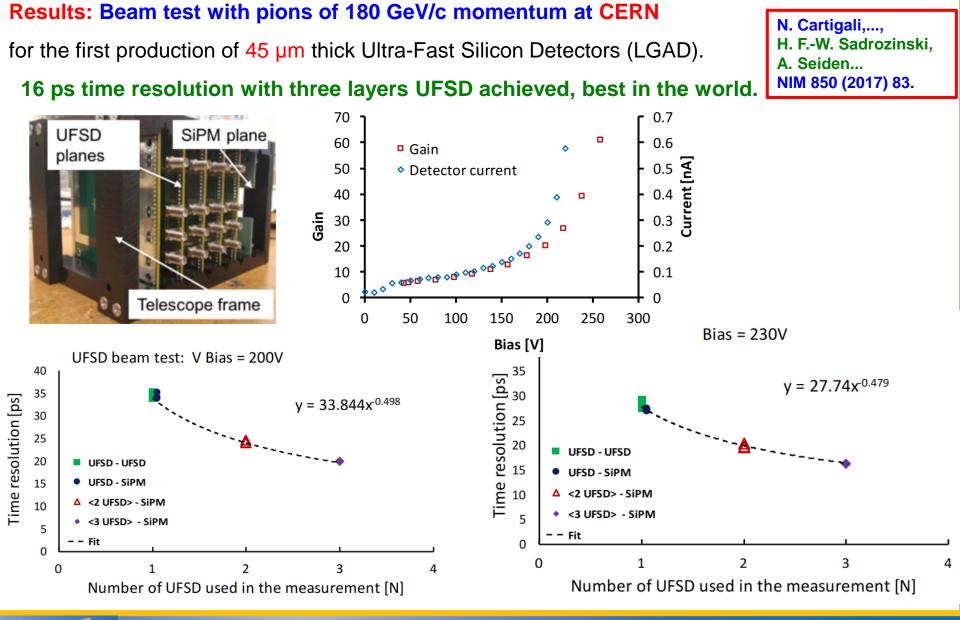

#### **UFSD: Beam Test at CERN**

Rachid Nouicer

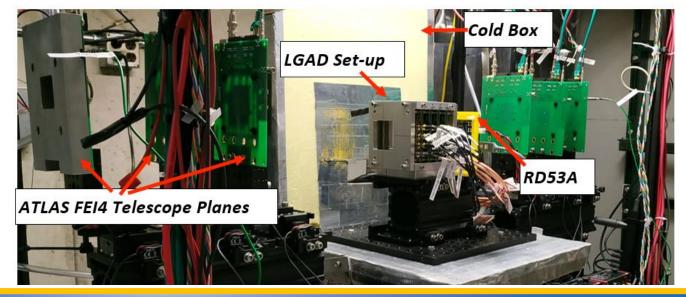

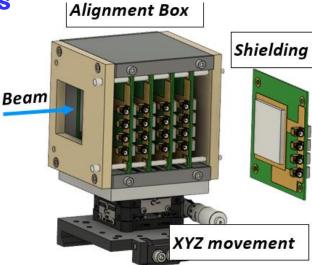

### **UFSD: Beam Test at Fermi Lab 2019**

#### Achieved by ANL (Argonne) and UC (Santa Cruz) groups

- Proton Beam with momentum 120 GeV

- Objective of evaluation of time resolution for minimum ionising particles and effect of more than one sensor plane

- Four LGAD sensors placed in alignment box mounted on XYZ stage

- Sensors HPK 1.2 (35μm), 3.1(50μm) were tested

- Cold temperature measurements at -30 °C is achieved using FP89-ME Julabo Chiller

- Data were collected in spills of 4 sec duration and instantaneous trigger rate between 1 and 5 Hz were achieved

**Courtesy of Manoj Jadhav**

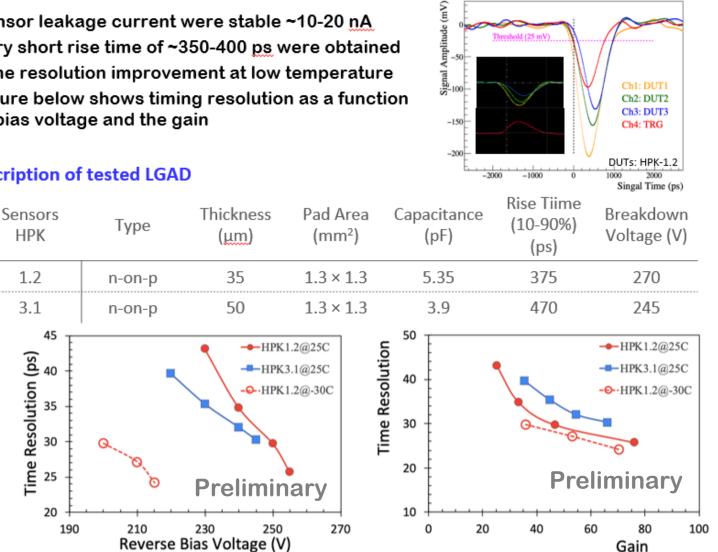

#### **UFSD: Beam Test at Fermi Lab 2019**

#### Achieved by ANL (Argonne) and UC (Santa Cruz) groups

**Courtesy of Manoj Jadhav**

Threshold (25 mV

#### **Timing Resolution**

- Sensor leakage current were stable ~10-20 nA

- Very short rise time of ~350-400 ps were obtained ٠

- Time resolution improvement at low temperature ٠

- Figure below shows timing resolution as a function of bias voltage and the gain

#### Description of tested LGAD

**Rachid Nouicer**

#### **UFSD: Beam Test at Fermi Lab 2019**

### Achieved by ANL (Argonne) and UC (Santa Cruz) groups

**Courtesy of Manoj Jadhav**

Timing Resolution: to be submitted for publication soon Normalised Entries Landau MPV Landau Width Gaussian Mear Gaussian Sig Achieved timing resolution of about 14.73 ps 0.22  $145.66 \pm 0.53$  $10.56 \pm 0.22$ 159.35 ± 0.49 25.91 ± 0.39  $116.53 \pm 0.70$  $10.11 \pm 0.31$ 129.07 ± 0.64  $24.70 \pm 0.55$ 0.2 Normalized signal amplitude vs. Bias Voltage ٠  $85.22 \pm 0.44$  $8.94 \pm 0.20$ 97.54 ± 0.51 22.20 ± 0.42 0.18 54.79 ± 0.59 7.93 ± 0.34 75.00 ± 0.67  $18.09 \pm 0.53$ Time Resolution vs. No. Of UFSDs 0.16 0.14 UFSD HPK-1.2 V<sub>bine</sub> = 255 V; Gain ~ 76 0.12  $V_{\text{bias}} = 240V$ Vbias = 255V  $V_{\text{bias}} = 215V$ ... = 250 V; Gain ~ 46 **HPK1.2** 0.1 V<sub>bine</sub> = 240 V; Gain ~ 33 (25 °C) (25 °C) (-30 °C) V<sub>bine</sub> = 230 V; Gain ~ 25 0.08 **Preliminary** 0.06 N = 134.78 ps 25.7 ps 24.17 ps 0.04 24.77 ps 18.79 ps N = 218.11 ps 0.02 0 50 100 150 200 250 300 350 400 15.04 ps 14.73 ps N = 3Signal Amplitude (mV) 40 40 UFSD beam test: Operating Temperature = 25 °C UFSD beam test: Operating Temperate 35 35 34.949x<sup>-0.48</sup> HPK-1.2 (35 μm)  $v = 29.382x^{-0}$ HPK-1.2 (35 μm) Time Resolution (ps) Fime Resolution (ps) 30 30 29.856x<sup>-0.490</sup> = 26.281x<sup>0.48</sup> 25.794x<sup>-0.473</sup> 25 25 = 24.263x<sup>-0.437</sup> 20 20 DUT-DUT: 255V OUT-DUT: 215V 15 O DUT-TRG: 255V 15 O DUT-TRG: 215V DUT-DUT: 250V DUT-DUT: 210V 10 10 **Preliminary** DUT-TRG: 250V **Preliminary** DUT-TRG: 210V DUT-DUT: 240V 5 5 DUT-DUT: 200V DUT-TRG: 240V DUT-TRG: 200V ٥ 0 Number of UFSDs (N), <N-UFSD> Number of UFSDs (N), <N-UFSD>

Rachid Nouicer

- > 3 layers UFSD (35  $\mu$ m) → 15 ps time resolution (measured)

- > Goal: UFSD (AC-LGAD) with 20  $\mu$ m thickness of sensor  $\rightarrow$  5 to 10 ps time resolution

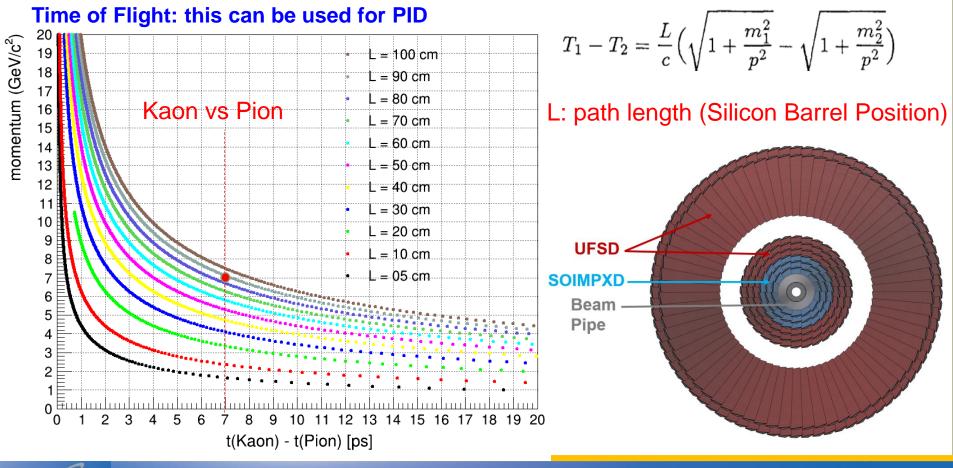

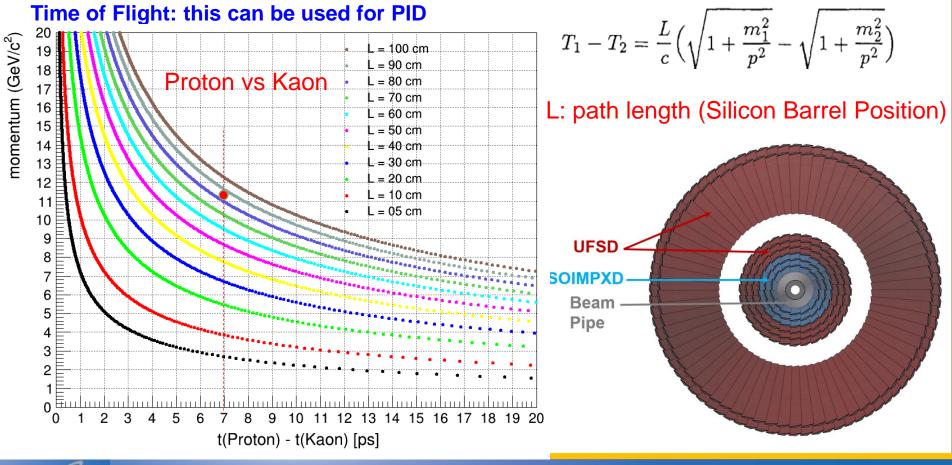

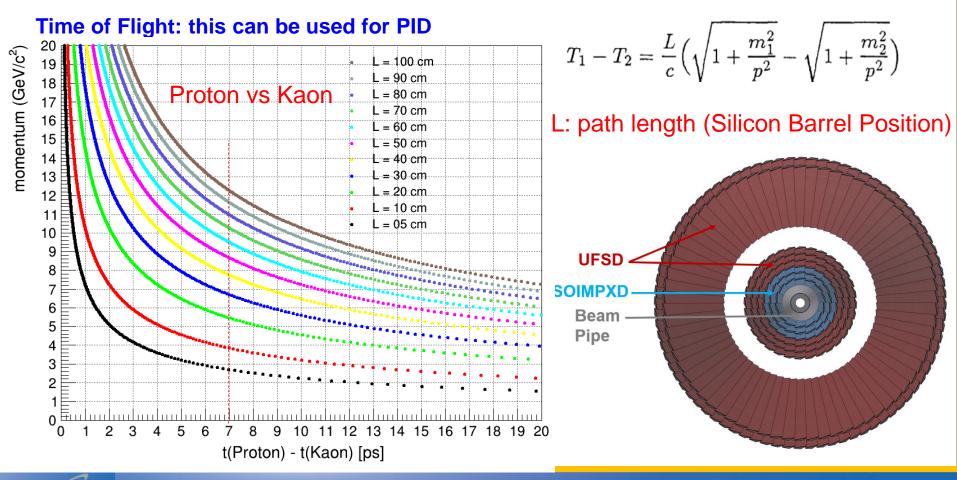

- Basic Math: Two particles with the same momentum but different masses have different

BROOKHAVEN

- > 3 layers UFSD (35  $\mu$ m) → 15 ps time resolution (measured)

- > Goal: UFSD (AC-LGAD) with 20  $\mu$ m thickness of sensor  $\rightarrow$  5 to 10 ps time resolution

- Basic Math: Two particles with the same momentum but different masses have different

BROOKHAVEN

# Simulation is needed to confirm PID with UFSD

BROOKHAVEN

Rachid Nouicer

# Summary

- Silicon-On-Insulator Monolithic PiXel

- **Detector (SOIMPXD) and Ultra-Fast Silicon**

- Detector (UFSD) provide best of silicon detector

- technology for tracking and particle

- identification:

- SOIMPXD: best position resolution < 1  $\mu$ m

- UFSD: best timing resolution < 16 ps (5 to 10 ps)

- SOIMPXD + UFSD = Silicon Hybrid Detector is state-of-art of silicon detector technology which EIC can use to search for new physics discoveries.