#### **Giacomo Contin**

Università di Trieste and INFN Sezione di Trieste

on behalf of the ALICE ITS3 Project

### Outline

- The ITS3 Project

- Detector motivations and layout

- Progress report on main R&D topics:

- Sensor development (see lain's talk later)

- Thinning, Bending, Interconnections

- Bent chip tests

- Mechanics

## ITS3 Project formation

ITS3 Project @ EICws - gia[https://indico.cern.ch/e/its3-kickoff]

Convision

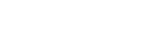

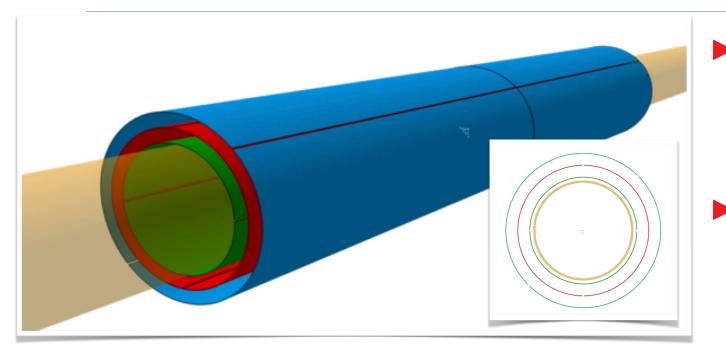

### ITS3 detector layout

replace

#### key improvements:

- ► closer to beam pipe: 23→18 mm

- less material:  $0.3 \rightarrow \sim 0.03 \% X_0$

#### main benefit:

- better tracking performance

- ► especially at low p<sub>T</sub>

#### based on:

- ► wafer-scale (up to ~28x10 cm),

- ► ultra-thin (20-40 µm),

- ▶ bent (R=18, 24, 30 mm) Si sensors (MAPS)

#### ITS3 Project @ EICws - giacomo.contin@ts.infn.it

2020-09-03

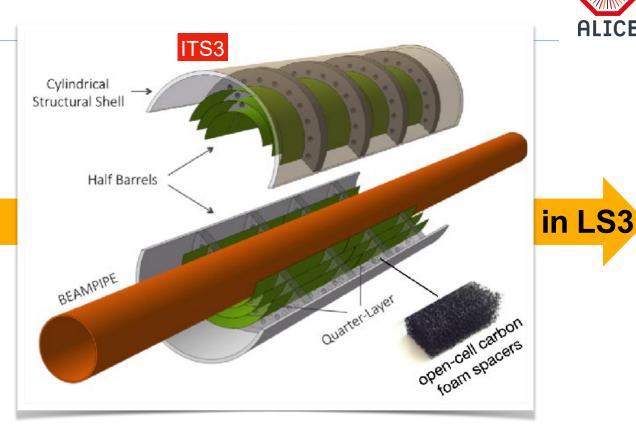

# ITS3 projected performance

#### improvement of factor 2 over all momenta

#### large improvement for low transverse momenta

5

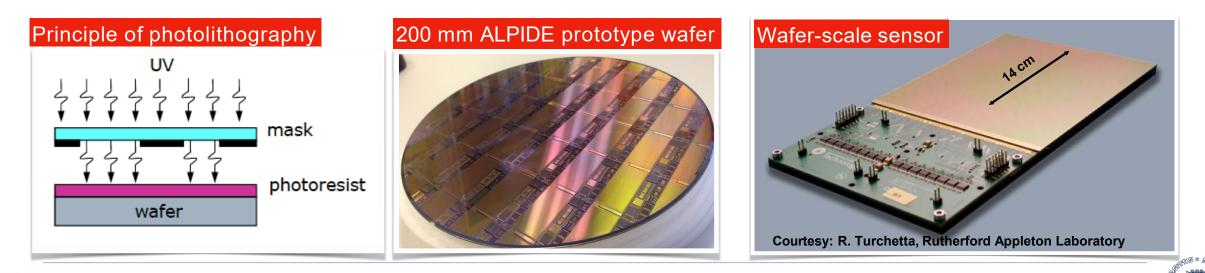

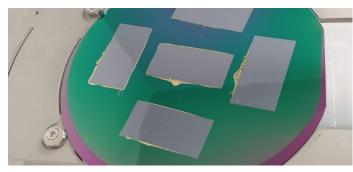

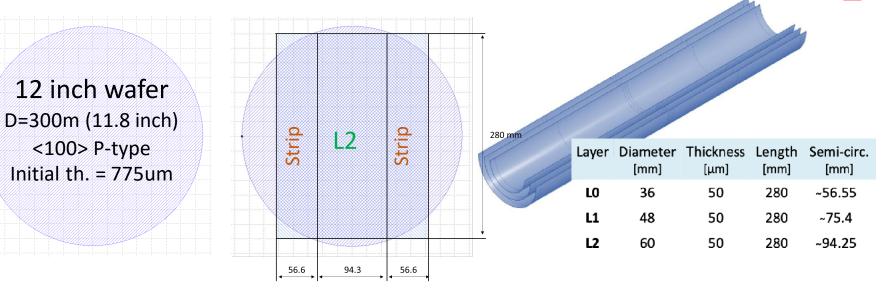

# Wafer-scale chip in 65 nm CMOS process

- Switch to TowerJazz 65 nm CMOS process (ITS2/ALPIDE: TowerJazz 180 nm)

- needed mainly because of larger wafers: Ø=300 mm (180 nm process only available on Ø=200 mm wafers)

- Stitching, i.e. producing chips as big as the wafer

- More details about the sensor development in the *next talk by lain Sedgwick*

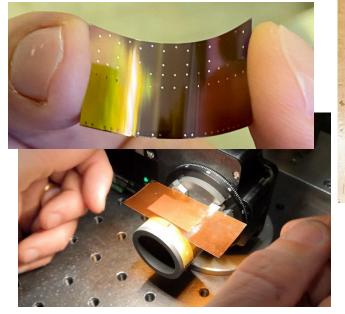

### R&D on bending and thinning

Manual bending

Bending tests

Controlled bending

Strain simulations

DRIE thinning tests

INF

7

8

SpTAB bonding

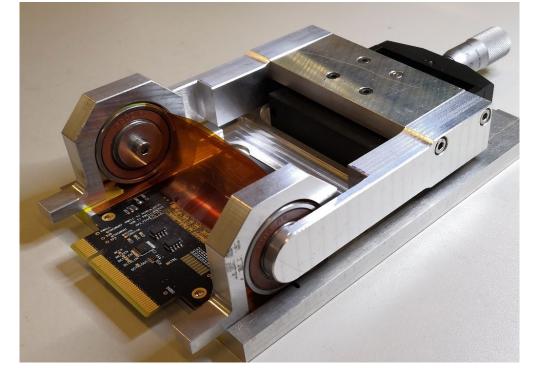

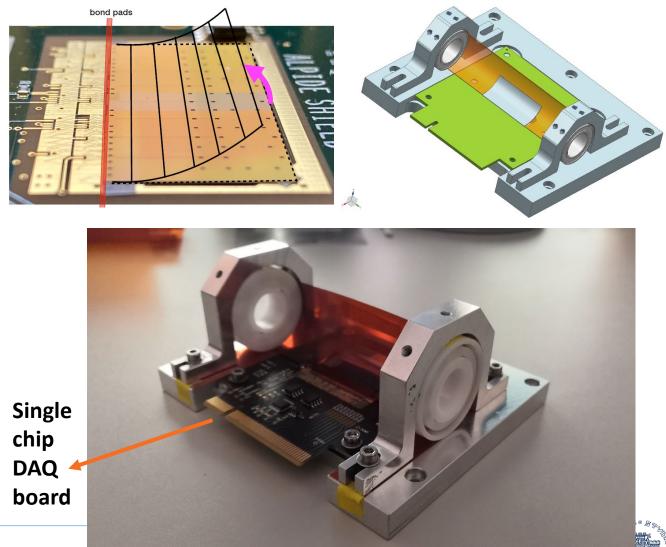

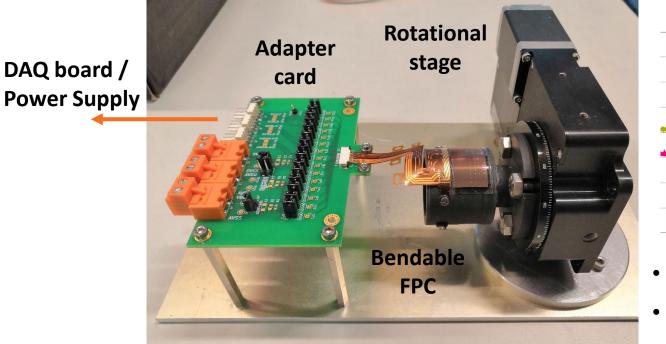

# Bending after bonding Bendable FPC Cylindrical bonding tool Wire bonding on curved surface Bonding after bending

Several support tools and flexible circuits

## Tools and procedures for interconnections

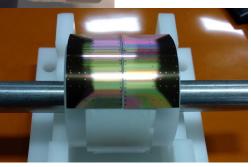

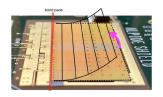

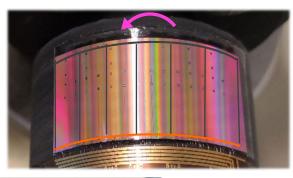

## Bent 50 $\mu$ m ALPIDE testing - 1

- Bent along the short side

- Bending affects pixel matrix only

- Bonding area is glued: flat and secured

- Variable curvature (down to 1 cm radius)

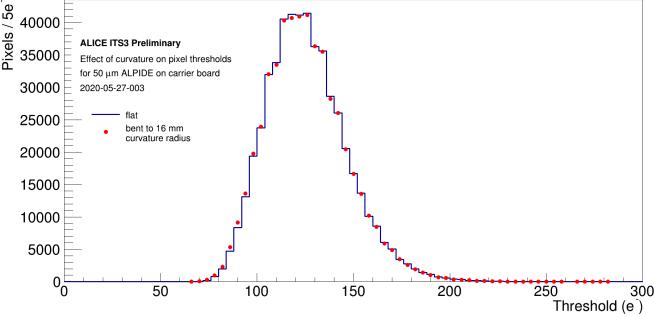

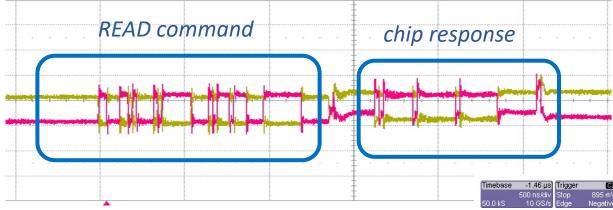

### Bent chip electrical tests

- Laboratory tests to characterize bent ALPIDEs in terms of thresholds and fake-hit rate

- different set-ups are tried

- experience on handling is gained

- The curvature effect is not noticeable on:

- pixel thresholds, FHR, pixel responsiveness

- tested down to below nominal bending radius

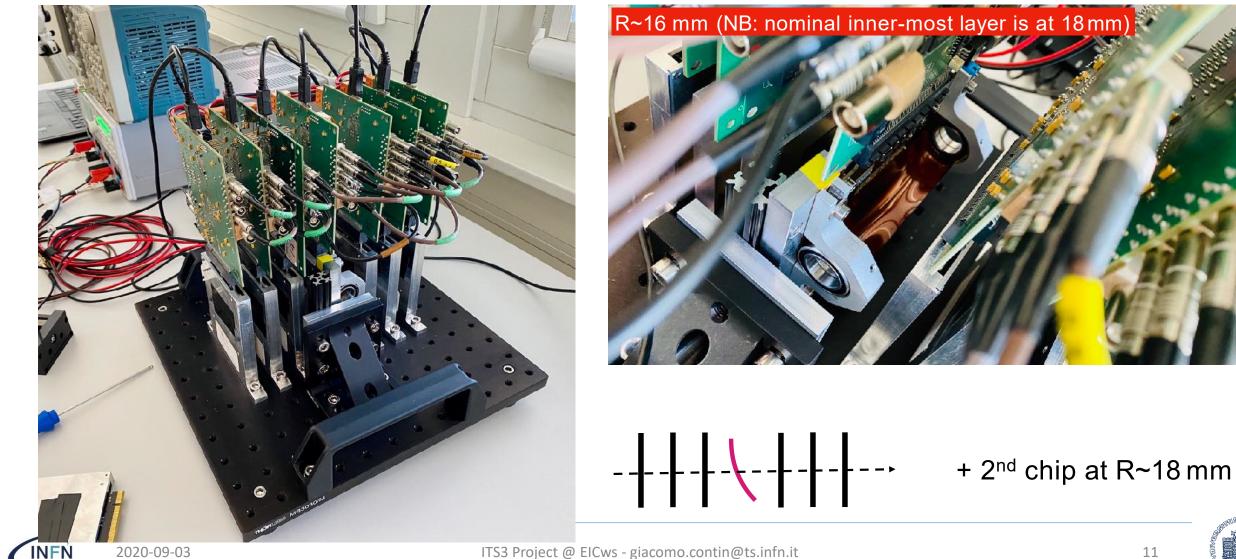

- 3 chips successfully installed and tested in lab, 2 of them sent to DESY for testbeam

50 µm-thick ALPIDE (sandwiched between to Kapton foils)

### Bent chip in ALPIDE-based beam telescope

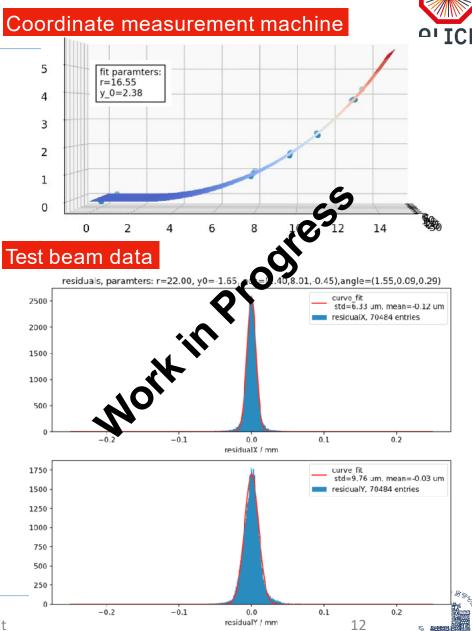

# Testbeam data analysis ongoing

- Bent chip shape approximated as a purely cylindrical segment

- First look at the efficiency shows >99.9% at nominal 100 e<sup>-</sup> threshold

- Main challenges:

- Describe the surface with µm-precision

- Hold the chip at the desired curvature:

- measurements before and after the test show a • curvature relaxation from 16 to 24 mm

- least squares optimization of the cylindrical model • vielded the DUT radius of 22 mm

- First paper in preparation

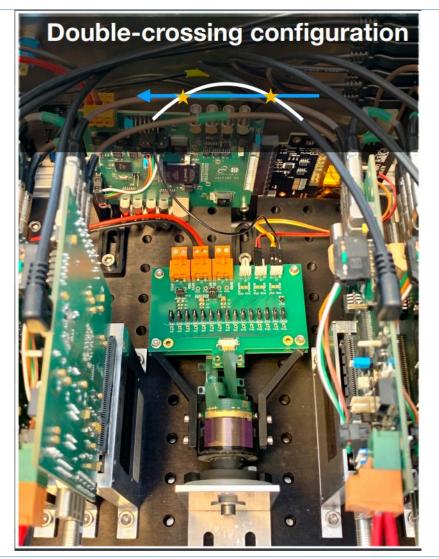

### Bent 50 µm ALPIDE testing - 2

#### Bent along the long side

- Affecting matrix and periphery

- Stretches the CMOS circuitry

- Completely glued onto support

- Fixed curvature (1.8 cm radius)

- Custom developed setup to interconnect the curved chip after bending

- I-V and response immediately checked after interconnecting the chip: works

- 5 chips successfully bent and tested.

- Handling tools to be improved to avoid accidents

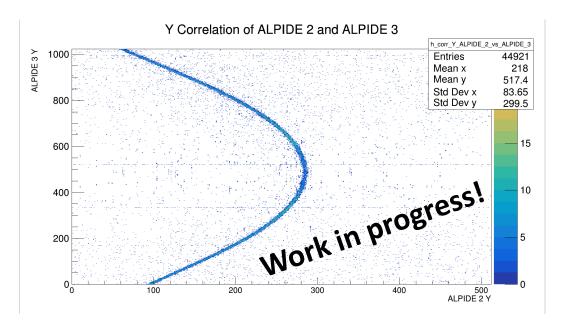

### Testbeam happened last week

Online monitoring Correlation bent chip – reference plane

Analysis is ongoing... but the bent chip works!

#### Towards the engineering module

Dummy chips: blank, 300 mm wafers were procured and thinned down to 50  $\mu$ m, under test

- they will serve first integration steps

- Next: adding a metallization layer with a heater for thermal tests

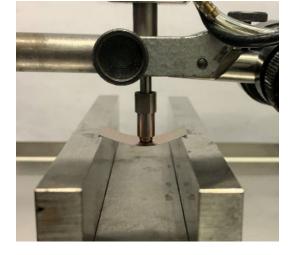

#### Carbon foam spacer development

| Company  | Foam Name | Material Ordered                                                                  | T.<br>val<br>ue<br>(CH<br>F) |            |

|----------|-----------|-----------------------------------------------------------------------------------|------------------------------|------------|

| ERG      | Duocel®   | 3 sets of rings + 1 sample                                                        | 2087                         | 10.06.2020 |

| ALLCOMP  | K9 Hi-K   | 1 set of rings + 1 sample for 2<br>different density (0.20-0.26<br>and 0.45-0.68) | 5360                         | 26.06.2020 |

| CFOAM    | 35HTC     | 3 sets of rings + 1 sample                                                        | 1500                         | 17.06.2020 |

| ENTEGRIS | POCO HTC  | 3 sets of rings + 1 sample                                                        | 2735                         | TBD        |

#### First spacers were machined

- The ITS3 Project has been endorsed by LHCC and has a fully operational organization

- R&D activities on the most challenging R&D topics are progressing well, and are generating interest beyond the ALICE community

- A new sensor based on 65 nm CMOS process is being developed (see next talk)

- Existing 50  $\mu m$  thick ALPIDEs have been bent and tested, demonstrating that an ITS3 based on bent silicon is possible

#### Thank you for your attention!

18

### Layout

| Beam pipe Inner/Outer Radius (mm)          | 16.0/16.5   |            |          |  |

|--------------------------------------------|-------------|------------|----------|--|

| IB Layer Parameters                        | Layer 0     | Layer 1    | Layer 2  |  |

| Radial position (mm)                       | 18.0        | 24.0       | 30.0     |  |

| Length (sensitive area) (mm)               | 300         |            |          |  |

| Pseudo-rapidity coverage                   | ±2.5        | ±2.3       | ±2.0     |  |

| Active area (cm <sup>2</sup> )             | 610         | 816        | 1016     |  |

| Pixel sensor dimensions (mm <sup>2</sup> ) | 280 x 56.5  | 280 x 75.5 | 280 x 94 |  |

| Number of sensors per layer                | 2           |            |          |  |

| Pixel size (µm²)                           | O (10 x 10) |            |          |  |

- New beam pipe:

- "old" radius/thickness: 18.2/0.8 mm

- new radius/thickness: 16.0/0.5 mm

- Extremely low material budget:

- Beam pipe thickness: 500 µm (0.14% X0)

- Sensor thickness: 20-40 μm (0.02-0.04% X0)

- Material homogeneously distributed:

- essentially zero systematic error from material distribution