### **TIGER ASIC for GEM Readout**

### Streaming Readout VI May 13-15, 2020

Istituto Nazionale di Fisica Nucleare

**Manuel Da Rocha Rolo**

The BESIIICGEM project has been funded by European Commission within the calls H2O2O-

MSCA-RISE-2014 and FEST RISE-MSCA-H2020-2020

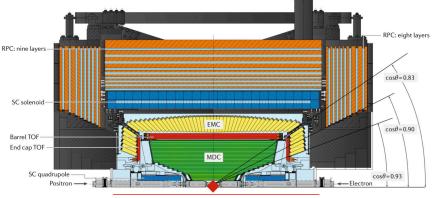

## The BESIII Experiment at BEPCII

The BESIII experiment @ BEPCII (Beijing Electron-Positron Collider) - operation since 1989, upgrade to BEPCII in 2008

BESIII Collaboration counts ~500 authors from 67 Institutions, 14 Countries

| Parameters                             | BEPCII                                |

|----------------------------------------|---------------------------------------|

| Center of mass Energy                  | $(2.0 \div 4.6) \text{ GeV}$          |

| Peak luminosity at $2 \times 1.89$ GeV | $\sim 10^{33} {\rm ~cm^{-2}  s^{-1}}$ |

| Circumference                          | 237.5 m                               |

| Number of rings                        | 2                                     |

| RF frequency                           | 499.8 MHz                             |

| Number of bunches                      | $2 \times 93$                         |

| Beam current                           | $2 \times 0.91 \text{ A}$             |

| Bunch spacing                          | $2.4/8 \text{ m}\mathrm{ns}^{-1}$     |

| Bunch length $(\sigma_z)$              | 1.5 cm                                |

| Bunch width $(\sigma_x)$               | $\sim 380 \ \mu { m m}$               |

| Bunch height $(\sigma_y)$              | $\sim 5.7~\mu{\rm m}$                 |

|                                        |                                       |

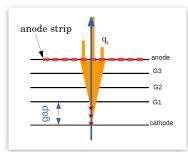

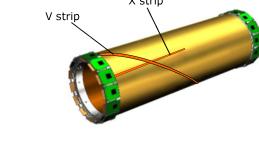

- new lightweight tracker based on an innovative Cylindrical Gas Electron Multiplier (CGEM) detector for the upgrade of the BESIII spectrometer

- analogue readout of the CGEM enables the use of charge centroid and µ-TPC algorithms to improve the spatial resolution

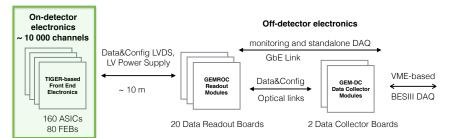

- 10 000 channels are readout by 160 dedicated 64-channel front-end ASICs

## Upgrade of the BESIII Inner Tracker

- Spatial resolution:  $\sigma_{xv}$  = 130  $\mu$ m ,  $\sigma_z$  = 300  $\mu$ m ٠

- Momentum resolution:  $\sigma_{nt}/p_{t} = 0.5\%$  @ 1 GeV/c ٠

- Efficiency = 98% •

- Material budget  $\leq$  1.5% of X<sub>0</sub> for all layers •

- Rate capability: ~10<sup>4</sup> Hz/cm<sup>2</sup>

- Coverage: 93%  $4\pi$

#### **Reconstruction algorithms**

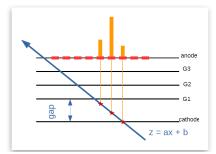

Weighted average of strip positions by collected charge μ-TPC readout

2D track reconstruction exploiting time of arrival and drift velocity

#### **TIGER ASIC for the CGEM-IT Readout**

- provides an analogue readout (time and charge information) for CC and  $\mu$ -TPC algorithms

- 64-channel Application Specific Integrated Circuit

# TIGER ASIC for the BESIII CGEM-IT

- TIGER has been designed for the readout of the CGEM-IT (Cylindrical Gas Electron Multiplier Inner Tracker)

- new inner tracker of BESIII Experiment

- 10 000 channels readout by 160 64-channel TIGER ASICs

- Time and charge measurements with fully-digital output

- Charge centroid and µ-TPC algorithms

- 130 µm spatial resolution with strip pitch of 650

- Sensor capacitance dependent on strips length, u

- Input charge: 2 50 fC

- Time resolution for µTPC mode: 5 ns

- Rate per channel: 60 kHz (4x safety factor)

- Power consumption: < 12 mW/ch</li>

- SEU-tolerant

| 0 µm         | $\sigma_{z}$      | 300 µm               |

|--------------|-------------------|----------------------|

| ıp to 100 pF | $\sigma_{pt}/p_t$ | 0.5% at 1 Ge         |

|              | Coverage          | 93% 4π               |

|              | Material budget   | < 1.5 X <sub>0</sub> |

|              | Inner radius      | 78 mm                |

|              | Outer radius      | 178 mm               |

|              | Magnetic field    | 1 T                  |

|              |                   |                      |

|              |                   |                      |

Efficiency

**Rate capability**

$\sigma_{r\Phi}$

98%

$10 \text{ kHz/cm}^2$

130 µm

at 1 GeV/c

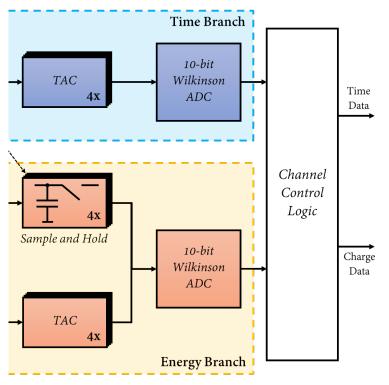

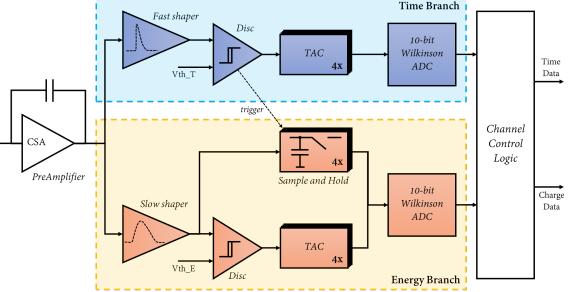

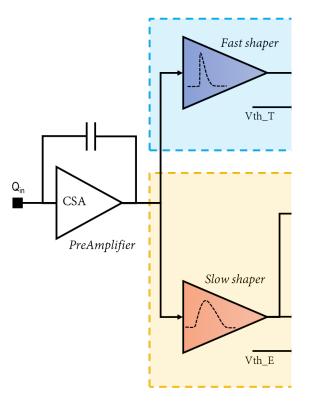

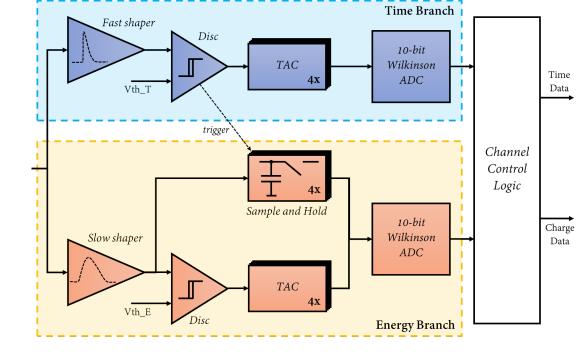

## **Channel Architecture**

- Analogue Front-End:

- Charge Sensitive Amplifier

- dual-branch shaper optimized for time and charge measurements

- Trigger-less readout architecture:

- 2 LE discriminators with 6-bit DAC for threshold equalization

- dual-threshold readout mode

- Timestamp on rising edge of fast branch

- Time resolution < 5 ns

- Low-power TDCs based on analogue interpolation

- Charge measurement:

- ToT: timestamp on rising/falling edge

- S/H: slow shaper output sampled and digitized with a 10-bit Wilkinson ADC

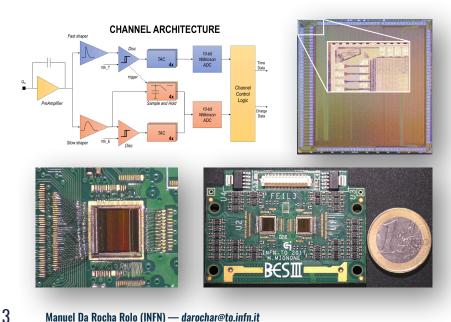

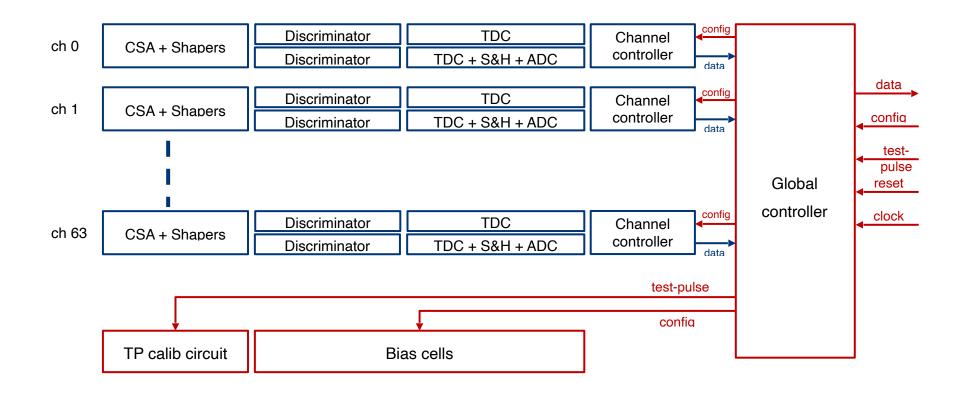

### **ASIC Architecture**

• The ASIC embeds an array of 64 channels (amplifier, discriminator, TDC/ADC), a digital global controller, bias and references generators and a test-pulse calibration circuit.

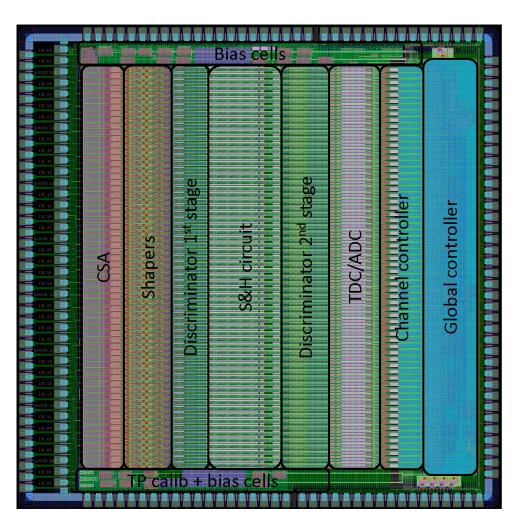

## **Chip Floorplan**

- 5 x 5 mm<sup>2</sup> 110nm CMOS technology

- Digital backend adapted from TOFPET2\* (SEU protected)

- 64 channels: CSA, shapers, TDC/ADC, local controller

- On-chip bias and power management

- On-chip calibration circuitry

- Trigger-less operation, fully digital output

- 160-200 MHz system clock

- 4 TX SDR/DDR LVDS links, 8B/10B encoding

- 10 MHz SPI-like configuration link

- Power consumption < 12 mW/ch

- Sustained event rate > 100 kHz/ch

## **Chip Test Board**

### Test-board for ASIC electrical characterization

- Trimming capability for analogue and digital power domains and external reference voltages

- Debug IO ports:

- 2. External test-pulse injection

- 3. External capacitor insertion

- 4. T-branch shaper output and threshold probe points (ch. 63)

- 5. Digital back-end control signals (TDC and S&H)

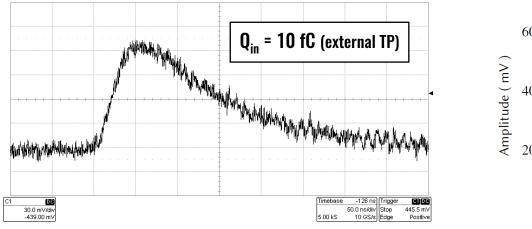

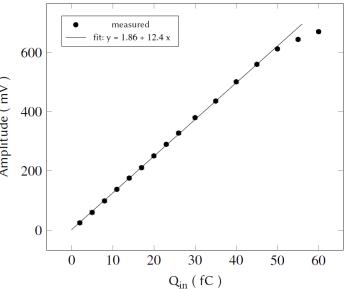

### **Electrical Characterization** Front-end response and linearity

Peaking time  $\approx 60$  ns

Gain ≈ 12.4 mV/fC

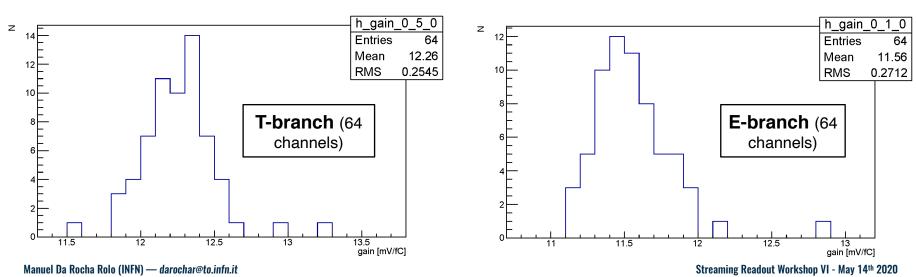

### **Electrical Characterization** Threshold scan and gain dispersion

- 1.  $V_{th}$  scan to generate LUT and equalize thresholds

- $\succ$  below 5 mV RMS dispersion after V<sub>th</sub> equalization

- 2. V<sub>th</sub> scan with internal TP to measure gain of 64 channels on both branches

#### 2. Gain dispersion

10

z <sup>50</sup>

45

40

35

30

25F

20

15

10

260

280

300

340

320

360

380

baseline [ mV ]

**1. Threshold**

Equalization

before equalization

after equalization

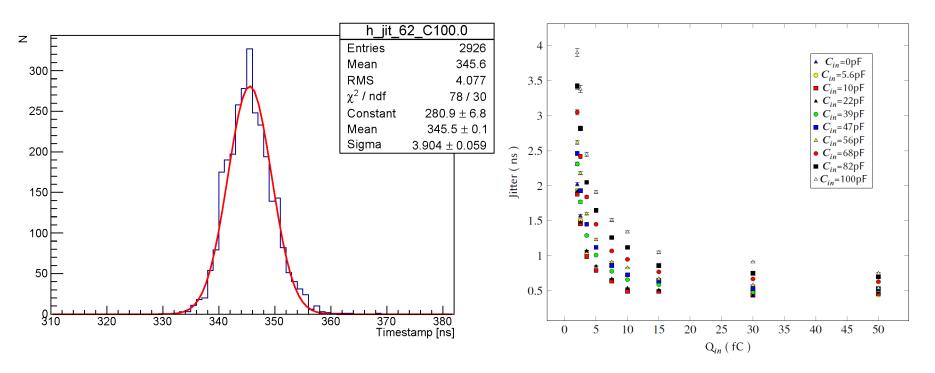

### **Electrical Characterization** Timing Resolution

- TP injected to VFE, generated by on-chip calibration circuit

- Here, fixed amplitude and time skew in respect to system clock

• Jitter vs. Qin vs. Cin

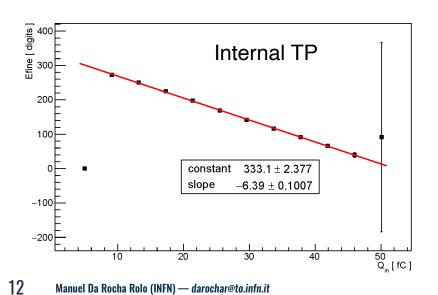

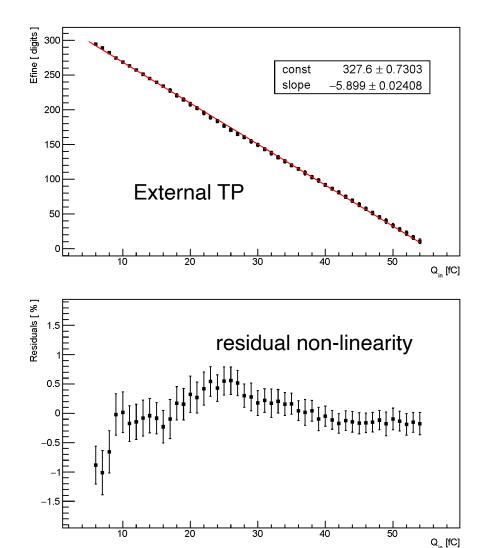

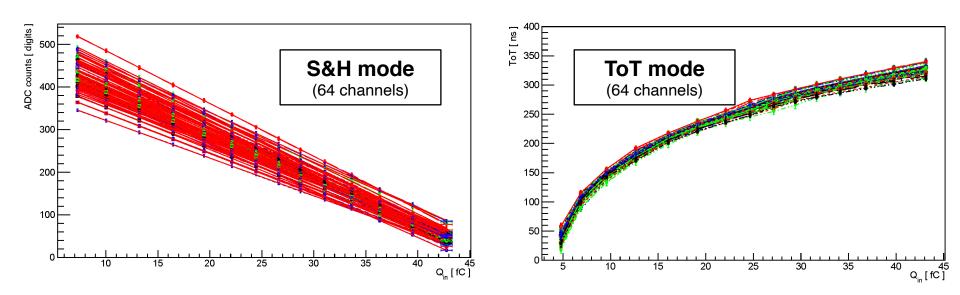

### Electrical Characterization Charge Measurement

- S/H dynamic range and linearity with external test-pulse generator (ch. 63 input debug port)

- Back-annotation for internal test pulse calibration to assess all channels

Streaming Readout Workshop VI - May 14th 2020

### Electrical Characterization Charge Measurement

- Linear response from S&H circuit easy to calibrate

- S&H limited by saturation of FE and ADC above 50 fC

- ToT response intrinsically not linear with CR-RC shapers

- ToT provides moderate energy resolution at low Qin, allows for extended dynamic range

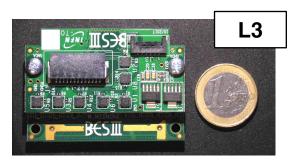

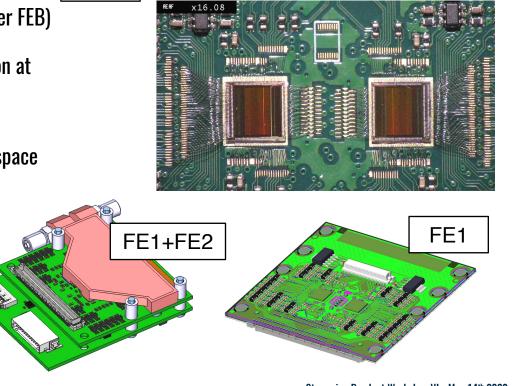

# **FEB (Front-End Board)**

**Front-End Board (FEB) for the on-detector CGEM electronics**

- Stack of two printed circuit boards:

- FE1: analogue-most layer

- FE2: digital layer  $\succ$

- 2 TIGER ASICs mounted on FE1 (128 channels per FEB)

- Water-cooling heat exchanger plate for operation at ۲ controlled temperature

- Different layout and routing for L3 FEBs due to space constraints inside BESIII

FE1

INFN TORINO

L1-L2

FE2

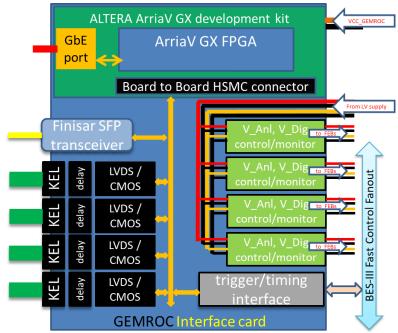

## **GEMROC (GEM ReadOut Card)**

- Developed by INFN Ferrara

- Off-detector electronics for the readout of the CGEM-IT detector (160 TIGER)

- Provides power, configuration and data interface to the TIGER ASICs (up to 8 TIGER for each GEMROC)

- Trigger-Matching operations (trigger-less mode also available)

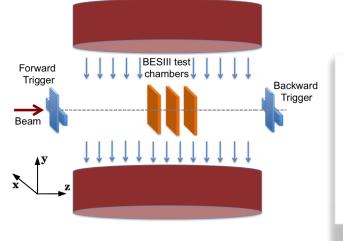

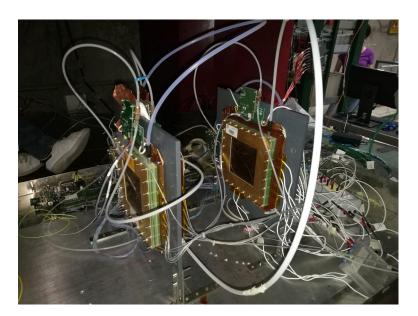

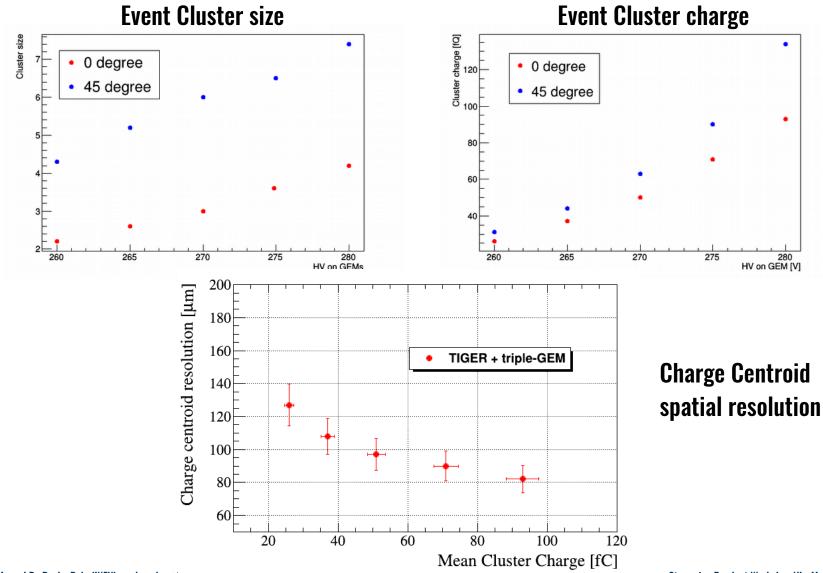

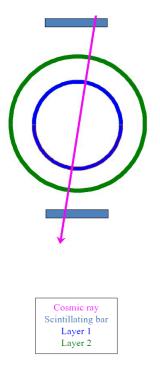

### **Beam tests with planar GEMs**

- 2 beam tests to validate the ASIC with the sensor:

- 10 x 10 cm<sup>2</sup> planar GEMs

- XY orthogonal strips

- Turin FPGA-based DAQ -> readout of 8 TIGER

- Nov 2017: Mainz Microtron (TIGER prototype version)

- Apr 2018: CERN H4 beam line (TIGER final version)

**Trigger-less readout:** trigger from scintillator bars injected as a digital test-pulse on one TIGER channel to be used as a reference for offline trigger-matching

### **Beam tests with planar GEMs**

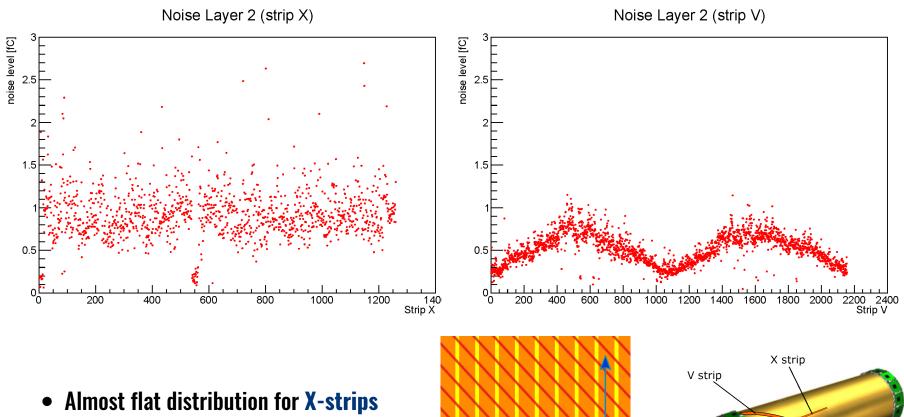

## Noise measurements on CGEM

V-strips noise follows the strips length

strips strips

Х

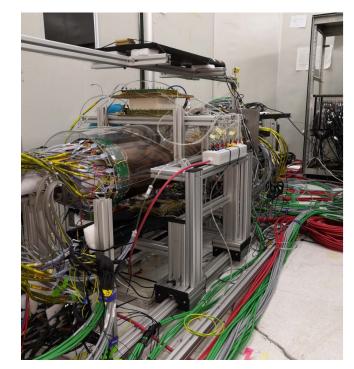

## CGEM-IT commissioning and tests

Two out of three layers of the CGEM-IT detector are assembled together and cosmic rays acquisitions are now ongoing at IHEP (Beijing, China)

- 88 TIGER ASICs readout by 11 GEMROC modules (>5000 electronics channels instrumented)

- GUFI (Graphical User Front-end Interface) software provides DAQ control tools for:

- Trigger-matched cosmic acquisition

- Trigger-less operation for periodic maintenance

R. Farinelli, "Preliminary results from the cosmic data taking of the BESIII cylindrical GEM detectors", talk at INSTR-20, Novosibirsk, Russia

### Thanks for your attention.

### Istituto Nazionale di Fisica Nucleare

Manuel Da Rocha Rolo INFN Torino

The BESIIICGEM project has been funded by European Commission within the calls H2020-MSCA-RISE-2014 and FEST RISE-MSCA-H2020-2020

### **Analog Front-End**

#### 1. CSA pre-amplifier

- Q<sub>in</sub> = 2 50 fC

- input transistor bias current set by 6-bit DAC (1.5 4.5 mA)

- ENC target < 2000 e<sup>-</sup> @ C<sub>in</sub> = 100 pF

#### 2. Time-branch

- Simple CR-RC shaper

- 60 ns peaking time for low-jitter timing measurement

#### 3. Energy-branch

- 4 complex-conjugate poles shaper for a more gaussian signal shape to reduce pile-up probability

- 170 ns peaking time for signal-to-noise ratio optimization

- BLH to lock the shapers output DC to an external reference value (V<sub>BL</sub> = 350 mV)

- ≻ Total gain ≈ 12 mV/fC

## **Trigerless Readout**

- LE discriminators with 6-bit DAC programmable thresholds and 3-bit DAC hysteresis

- Data-push readout architecture: each signal above the selected threshold is taken as a good event, digitized and sent off-chip (no external trigger)

### **Time and Charge Measurement**

- Coarse time measurement from the chip master clock counter

- Fine time measurement with low-power analogue TDCs based on time interpolation (I.F. = 128)

- 50 ps time binning @ 160 MHz

- Quad-buffered TACs for event de-randomization

- TAC buffers with refresh scheme to avoid off-chip correction algorithm for leakage

- Charge measurement with S/H circuit sampling the E-branch shaper output

- Programmable sampling time targeting the signal peak

- Digitization with Wilkinson ADC shared with the TDC

- Quad-buffered sampling capacitors for event de-randomization

- Charge measurement from ToT information by operating both branches in TDC mode (backup solution)