### **Streaming Readout Grand Challenge**

### **TDIS Streaming Readout Prototype**

Eric Pooser Jefferson Lab

07/09/2019

On Behalf of the TDIS SRO Working Group

# **TDIS Streaming Readout Prototype**

- TDIS = Tagged Deep Inelastic Scattering

- Hall-A, Super Big-Bite (SBS)

- Measure high W<sup>2</sup>, Q<sup>2</sup> electron-meson scattering events

- A GEM based radial time projection chamber (TPC) will facilitate the detection of low momentum spectators

- ALICE collaboration (CERN) is currently upgrading their TPC with a GEM based detection system that is read out continuously

- Streaming readout (SRO)

- Continuous time ordered sequences of detector system readout

- ~1 TB/s post zero-suppression

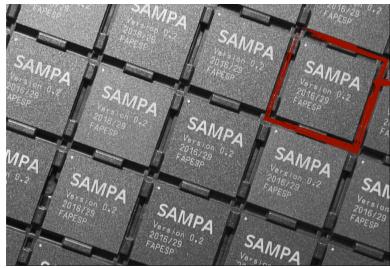

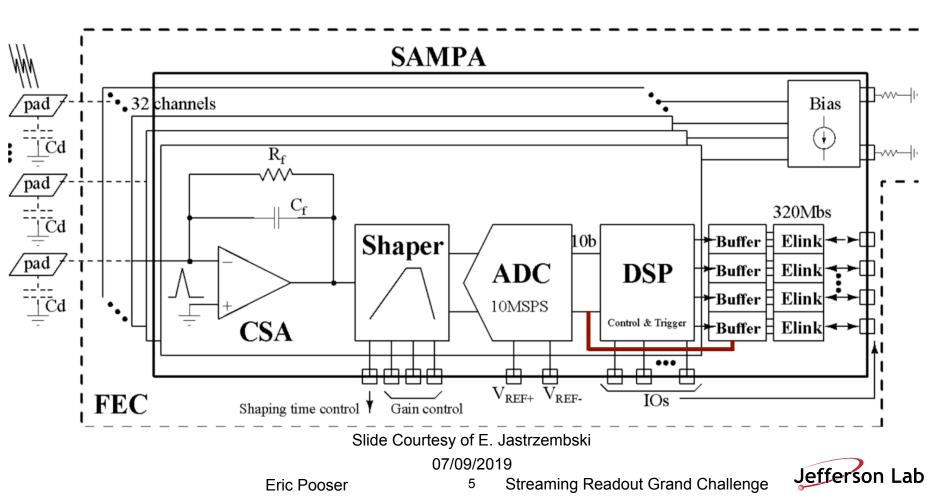

- Novel front-end ASIC was developed specifically for this purpose - SAMPA

- We are interested in exploring how experiments at JLab can take advantage of this technology as well as the SRO concept

- SRO Grand Challenge

\*LHCb will move to a triggerless-readout system for LHC Run 3 (2021-2023), and process 5 TB/s in real time on the CPU farm.

07/09/2019

Eric Pooser

- 2

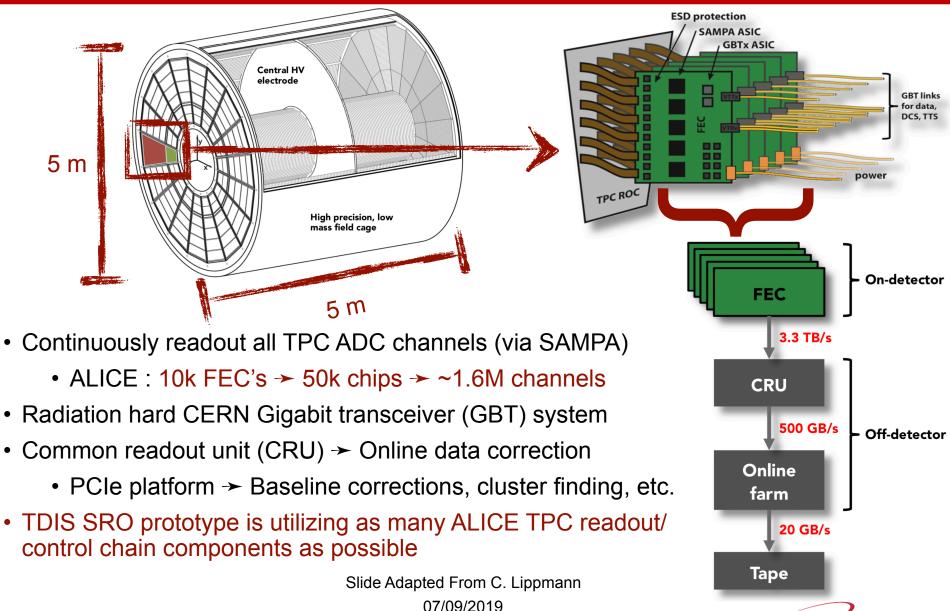

# ALICE TPC SRO Strategy

Eric Pooser

3 Streaming Readout Grand Challenge

Jefferson Lab

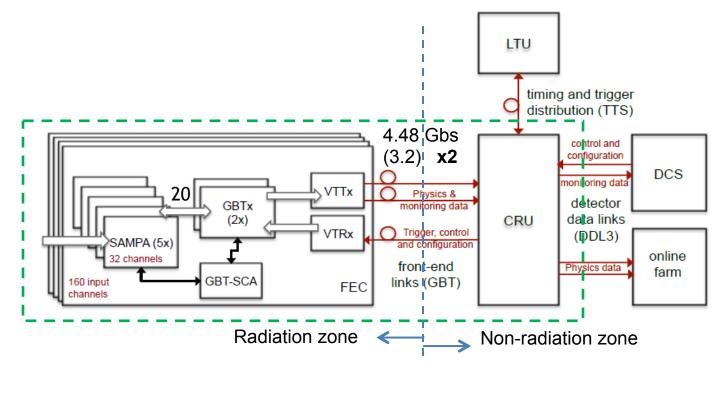

# **ALICE SRO Electronics**

- SAMPA : University of São Paulo, Brazil

- Supports both continuous and triggered readout modes

- Digital signal processor (can be bypassed)

- Single ALICE front end card (FEC) supports 5 SAMPA chips (160 channels)

- Serialized data are routed via e-links into 2 GBTx chips which drive fiber transmitters (VTTx) at 3.2 Gb/s each

Slide Adapted From C. Lippmann 07/09/2019

Eric Pooser

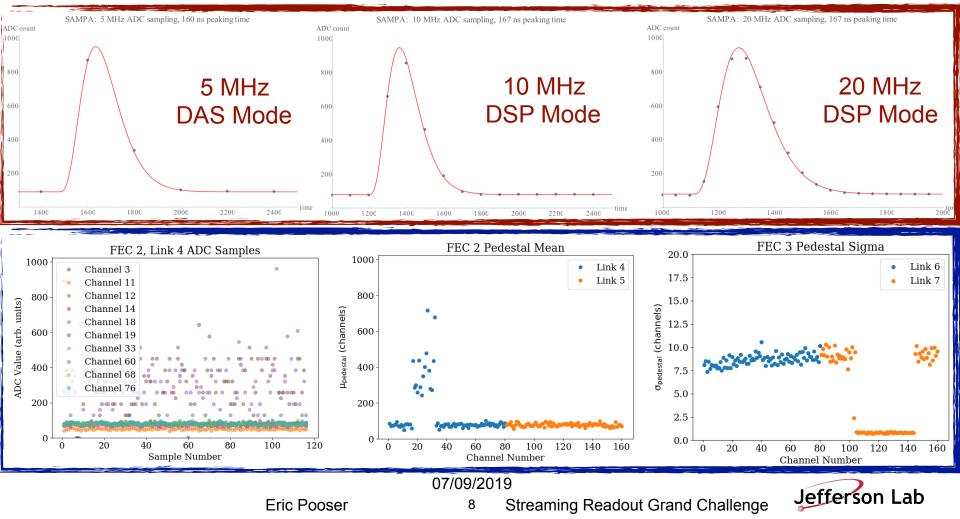

#### **SAMPA Operational Modes**

- Direct ADC serialization (DAS) mode → bypass digital signal processor (DSP)

- ALICE FEC design limits ADC rate to 5 MHz in DAS mode → 10 e-links (max 3.2 Gb/s)

- DSP mode → pedestal subtraction, baseline corrections, zero-suppression, compression

- Sampling rates of 10 or 20 MHz → 11 e-links (max 3.2 Gb/s or 6.4 Gb/s)

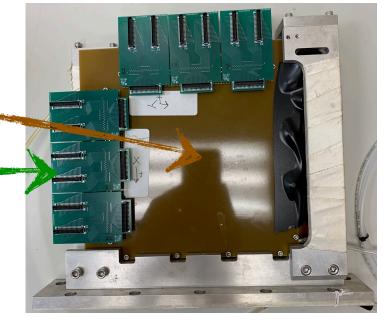

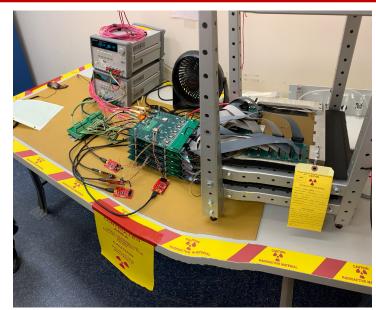

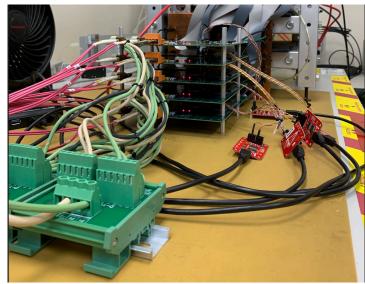

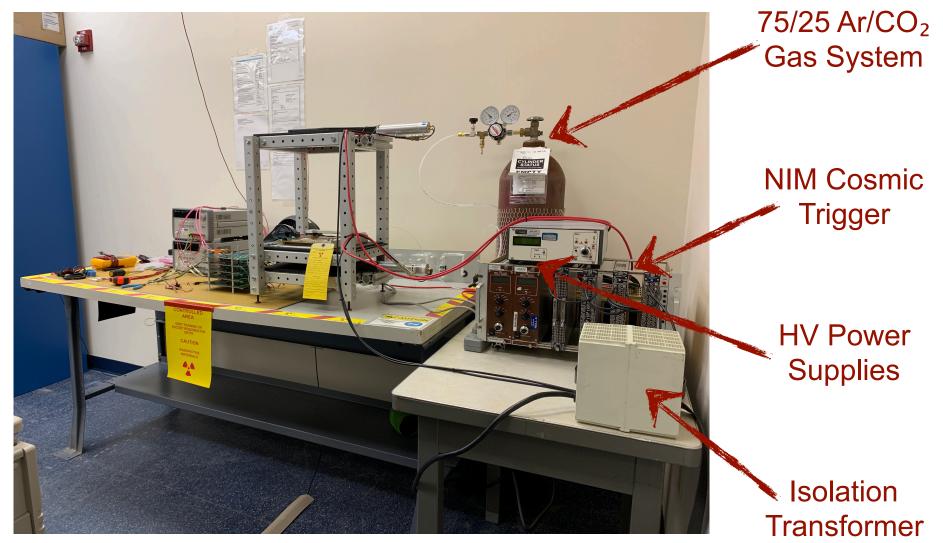

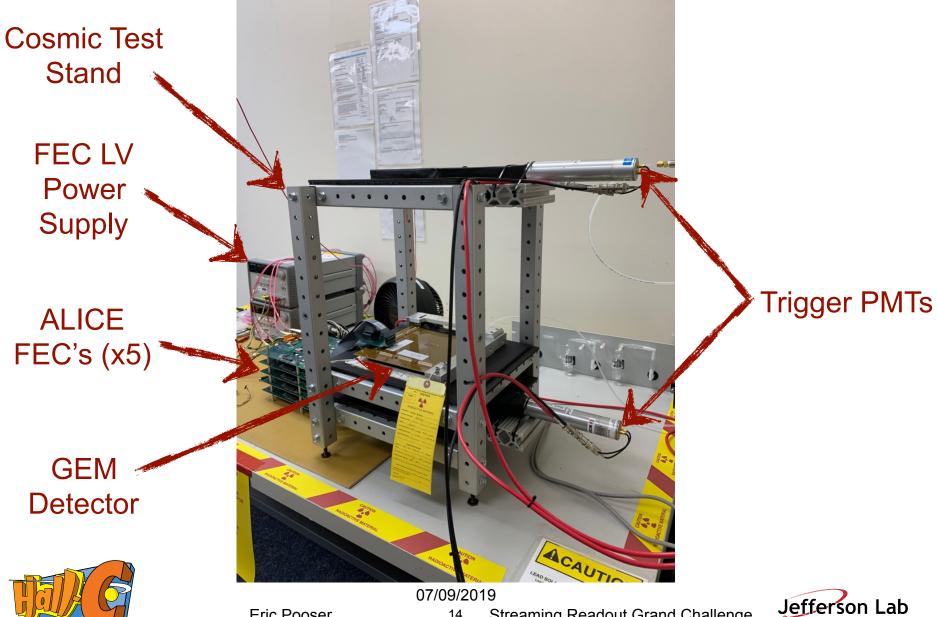

# **TDIS SRO Prototype**

- INDRA-ASTRA Facility (CC F110)

- Variety of hardware present so that it is "streaming capable"

- User programmable network switch with 100 Gb/s data link

- Fast multi-core server machine with 100 Gb/s data link

- Fast PC's with several PCIe slots for testing high speed data links, FPGAs, GPU's, etc.

- Triple-GEM detector provides 768

channels of analog data

- Custom transition card fabricated to facilitate ALICE FEC inputs

- 800 channels of SAMPA readout (5 FEC's, 25 SAMPA chips) via ALICE SRO system

07/09/2019

Eric Pooser

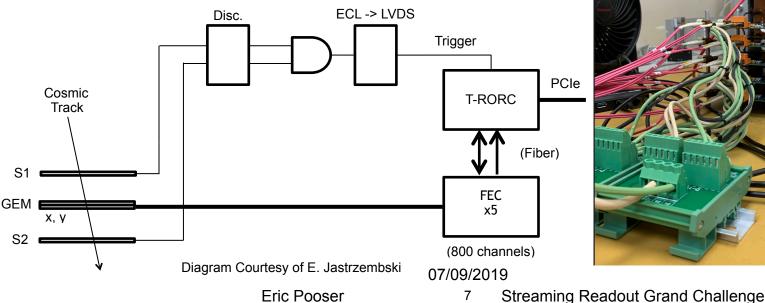

# **TDIS SRO Prototype**

- Currently we are streaming trigger-less GEM data (768 channels) in DAS mode at 45 Gb/s via 5 ALICE FEC's

- GEM → FEC → TRORC (30 Gb/s) → PC Memory → Disk

- By implementing the receipt of a trigger, a programmable window of streamed data can be captured by the T-RORC

- Keeps the data volume to memory (and to disk) at a manageable level

- Will modify the T-RORC firmware to suppress the transmission of unnecessary sync packet data to memory and disk

- Sync packets keep the serial links from the SAMPAs active when there is no hit data to send

- Then we can acquire data in a truly continuous fashion

Jefferson Lab

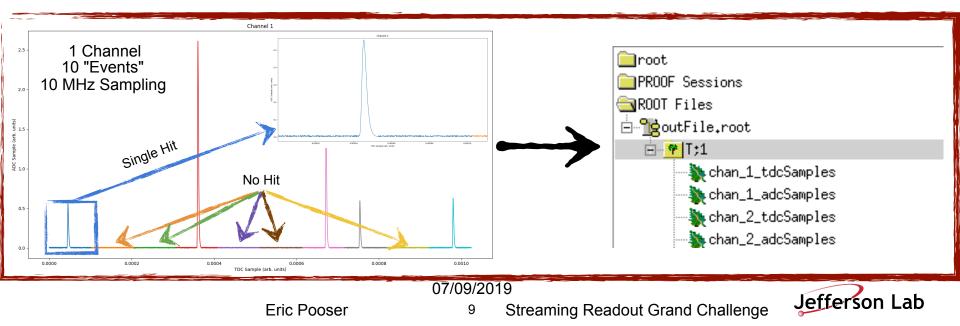

### **TDIS SRO SAMPA Data**

- Variety of ways to analyze/monitor the data are actively being developed

- SAMPA response to test pulse → 5 MHz, 10 MHz, and 20 MHz

- TDIS SRO GEM data  $\rightarrow$  5 MHz DAS mode  $\rightarrow$  sample,  $\mu_{ped}$ , and  $\sigma_{ped}$  data

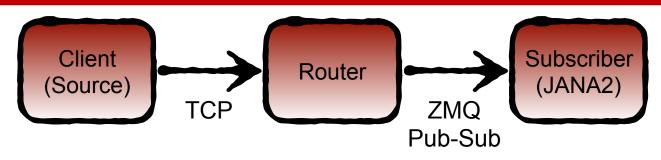

### **TDIS SRO Data Transfer Protocol**

- Router receives data from emulator or hardware sources and publishes data to subscribers (analyzers) - SAMPA SRO emulator and JANA2 plugin have been developed

- Open source ZeroMQ library was chosen as the publish-subscribe data transport between the router and the subscriber → Mature library that is well maintained and is evolving

- INDRA-Streaming software exists and is actively being developed to interface with JANA2

# **Looking Forward**

- Reduce observed noise as much as possible in TDIS SRO prototype

- Improve ground connection between FEC and GEM, EM shielding

- Integrate cosmic trigger into SRO DAQ

- NIM → LVDS conversion, configure SAMPA trigger latency

- Configure SRO DAQ for zero-suppression (DSP mode) operation

- Create pedestal/threshold database

- Suppress non-data sync headers and reformat hit data

- Develop T-RORC firmware to stream only hit data to memory

- Integrate FELIX readout hardware and software

- Utilize FELIX software to configure FEC hardware

- Complete the chain of SRO

- TIDIS SRO Prototype → Router → JANA2 Subscriber → JupyterLab

- Special thanks to: E. Jastrzembski, J. Wilson, A. Hellman, C. Long, et al.

# Backup Slides

07/09/2019

Eric Pooser

#### **TDIS SRO Test Stand Setup**

07/09/2019

lenge Jefferson Lab

Eric Pooser

#### **TIDIS SRO Test Stand Setup**

Eric Pooser

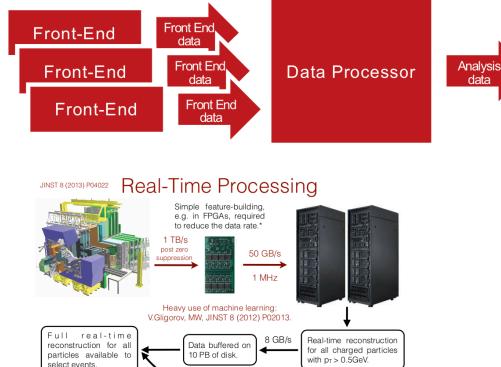

### **TDIS Streaming Readout Prototype**

Detectors

Readout

Analysis data

#### **Traditional triggered readout**

- data is digitized into buffers and a trigger, per event, starts readout

- parts of events are transported through the DAQ to an event builder where they are assembled into events

- event selection based on fast detectors with coarse resolution

#### default at JLab experiments

#### **Streaming readout**

- · data is read continuously from all channels

- data then flows unimpeded in parallel channels to storage or a local compute resource

- event selection based on full detector information

#### intended for TDIS, SoLid, EIC

Slide Courtesy of M. Diefenthaler

07/09/2019

Eric Pooser

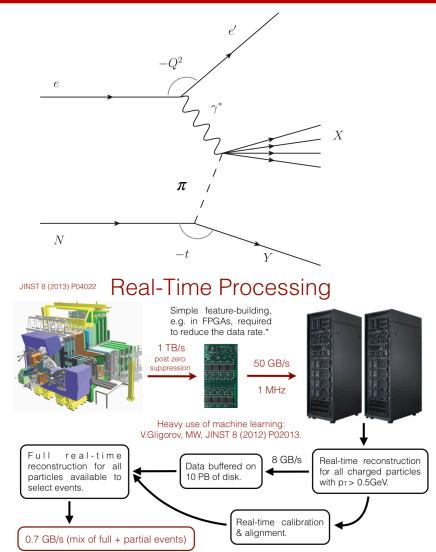

# **TDIS Streaming Readout Prototype**

#### **Data Processor**

- assembles the data into events

- outputs data suitable for final analysis (Analysis data)

#### Features (among others)

- · ideal for machine learning

- automated calibration and alignment

- partial or full event reconstruction

- event selection and/or labeling into analysis streams

- automated anomaly detection

- responsive detectors (conscious experiment)

\*LHCb will move to a triggerless-readout system for LHC Run 3 (2021-2023), and process 5 TB/s in real time on the CPU farm.

0.7 GB/s (mix of full + partial events)

Slide Courtesy of M. Diefenthaler

07/09/2019

Eric Pooser

Real-time calibration & alignment.

#### **ALICE SAMPA Specifications**

| Specification                   | TPC                  | МСН                 |

|---------------------------------|----------------------|---------------------|

| Voltage supply                  | 1.25 V               | 1.25 V              |

| Polarity                        | Negative             | Positive            |

| Detector capacitance (Cd)       | 18.5 pF              | 40 pF - 80 pF       |

| Peaking time (ts)               | 160 ns               | 300 ns              |

| Shaping order                   | 4th                  | 4th                 |

| Equivalent Noise Charge (ENC)   | < 600e@ts=160 ns*    | < 950e @ Cd=40 pF*  |

| i i                             |                      | < 1600e @ Cd=80 pF* |

| Linear Range                    | 100 fC or 67 fC      | 500 fC              |

| Sensitivity                     | 20 mV/fC or 30 mV/fC | 4 mV/fC             |

| Non-Linearity (CSA + Shaper)    | < 1%                 | < 1%                |

| Crosstalk                       | < 0.3%@ts=160 ns     | < 0.2%@ts=300 ns    |

| ADC effective input range       | 2 Vpp                | 2 Vpp               |

| ADC resolution                  | 10-bit               | 10-bit              |

| Sampling Frequency              | 10 (20) Msamples/s   | 10 Msamples/s       |

| INL (ADC)                       | <0.65 LSB            | <0.65 LSB           |

| DNL (ADC)                       | <0.6 LSB             | <0.6 LSB            |

| ENOB (ADC)**                    | > 9.2-bit            | > 9.2-bit           |

| Power consumption (per channel) |                      |                     |

| CSA + Shaper + ADC              | < 15 mW              | < 15 mW             |

| Channels per chip               | 32                   | 32                  |

$R_{esd} = 70\Omega$

\*\* @ 0.5MHz, 10Msamples/s

Slide Courtesy of E. Jastrzembski

07/09/2019

Eric Pooser

### **ALICE System**

- FEC Front End Card (160 ch / FEC)

- CRU Common Readout Unit ~12 FECs / CRU = ~1920 ch / CRU

- DCS Detector Control System

- LTU Local Trigger Unit

Slide Courtesy of E. Jastrzembski

07/09/2019

Eric Pooser

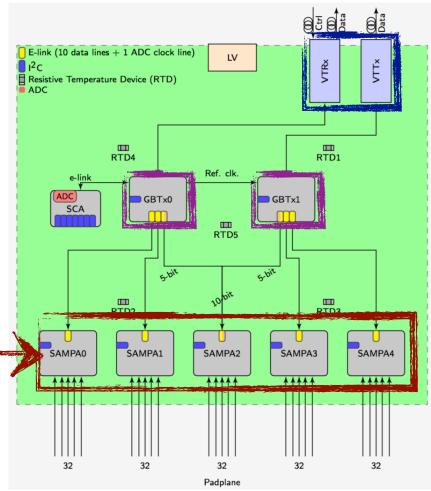

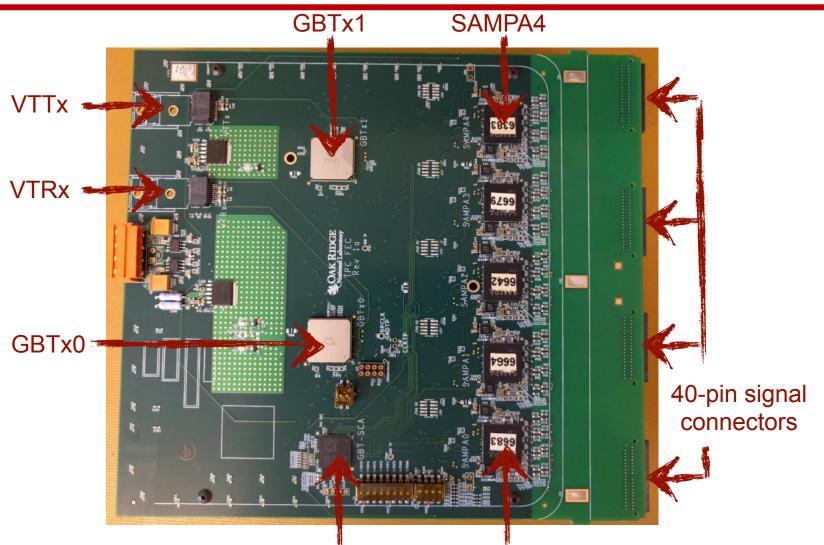

#### ALICE FEC (JLab Version)

Slide Courtesy of E. Jastrzembski

**GBT-SCA**

07/09/2019

Jefferson Lab

Eric Pooser

19 Streaming Readout Grand Challenge

SAMPA0

#### **C-RORC (Common Readout Receiver Card)**

#### Xilinx Virtex-6 FPGA

3x QSFP: 12 fast serial links connected to FPGA transceivers (GTX) Up to 6.6 Gbps per channel

PCIe Gen2, 8 Lanes 8x 5.0 Gbps, connected to Xilinx PCIe Hard Block

(~ 30 Gb/s)

Slide Courtesy of E. Jastrzembski

07/09/2019

Eric Pooser

07/09/2019

Eric Pooser