#### Multi-Channel Readout ICs Development Status

#### **Streaming Readout Meeting**

December 2, 2018

Phaneendra "Phani" Bikkina, Principal Design Engineer <u>Phaneendra.Bikkina@alphacoreinc.com</u>

> Daniel Mazidi, Design Engineer Daniel.Mazidi@alphacoreinc.com

Esko Mikkola, CEO Esko.Mikkola@alphacoreinc.com

Alphacore Inc. | www.alphacoreinc.com | Copyright © 2018 | SBIR DATA RIGHTS 1

Founded in 2012 and located in Arizona's "Silicon Desert"

- Providing technology that enable major advances in:

- Homeland Security

- Defense

- Aerospace

- Scientific Research

- Medical Imaging

- Product areas span:

- High performance analog and mixed signal

- High-speed visible light and infrared camera systems

- Radiation-hard electronics

2

### **Alphacore's Team**

Alphacore's team is a combination of engineering and business professionals with long histories of delivering products and services to customers who demand state-of-the-art performance.

Our team has had successful careers at companies ranging from start-ups to multinationals including **Raytheon**, **Texas Instruments, Analog Devices**, **Bell Labs, Intel, United Technologies**, and **Honeywell**.

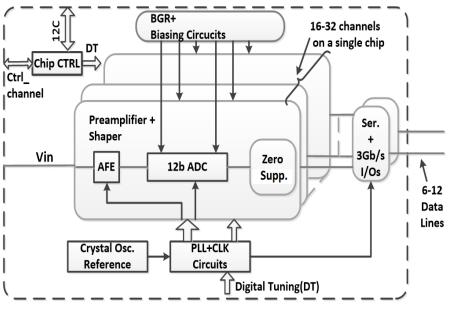

## Multi-Channel Readout IC for Nuclear Physics Experiments

#### The need

"Universal", low-cost, highperformance, readout integrated circuits (ROICs) for several planned nuclear physics experiments

DOE STTR Phase II

Key features include:

- 1-channel, 8-channel and 16-channel ICs

- Three types of ICs: 1) Preamplifiers, 2) ADCs and 3) Combined ROICs

- 300-800ENC CSA preamplifier for Cd = 0 -50pF

- 1,300ENC current conveyer preamplifier for Cd = 0 - 300pF

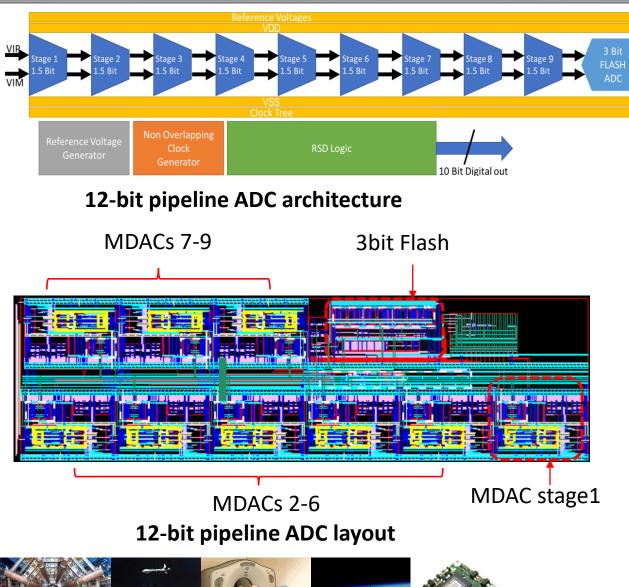

- 12-bit pipeline ADC, 100-200 MSPS, 70mW

- 10-bit pipeline ADC, 50-100 MSPS, <10mW

- Low-cost 180nm CMOS fabrication TID > 300krad

- SEL, SEU, SEFI hardened

- Non-ionizing energy loss (NIEL) > 2\*10<sup>13</sup>

- First full engineering run tape out finalized in September 2018 in the XFAB 180nm process

- Chips coming back for testing in January 2019

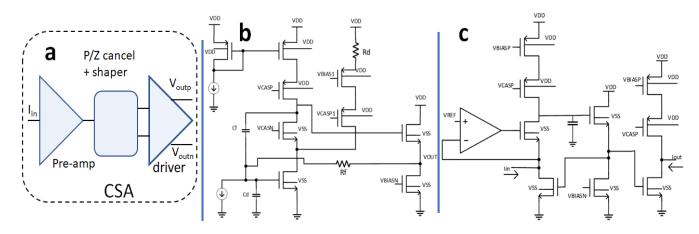

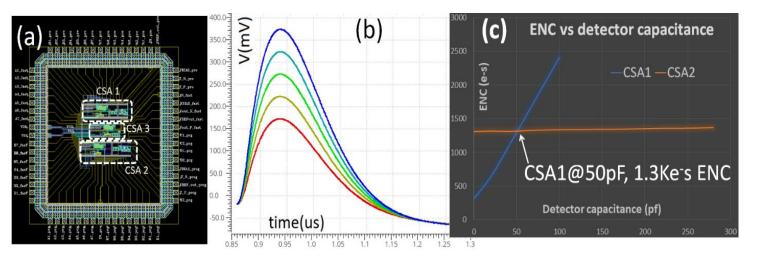

## **Preamplifier Info**

Figure 1: (a) Alphacore's preamplifier architecture, (b) CSA1 charge sensitive preamp + shaper (c) CSA2, current conveyer amplifier + shaper

Figure 2: a) Alphacore's test chip to characterize the CSAs b) transient simulations of CSAs for varying input current pulses c) comparison of ENC of CSA1 and CSA2.

5

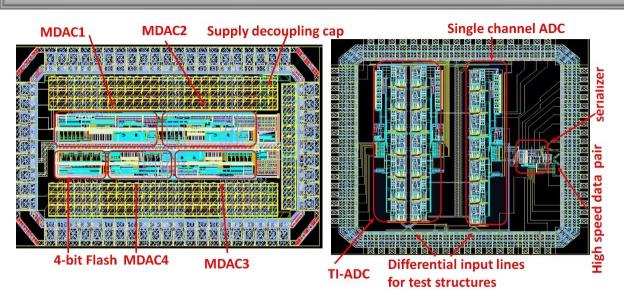

### ADC Info

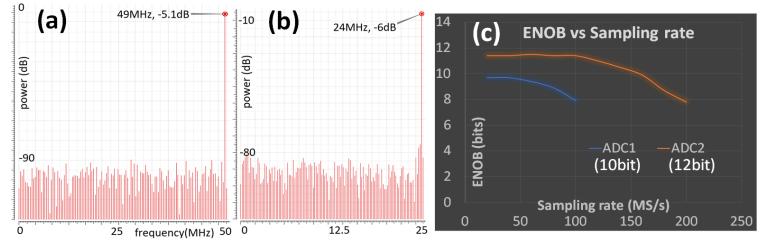

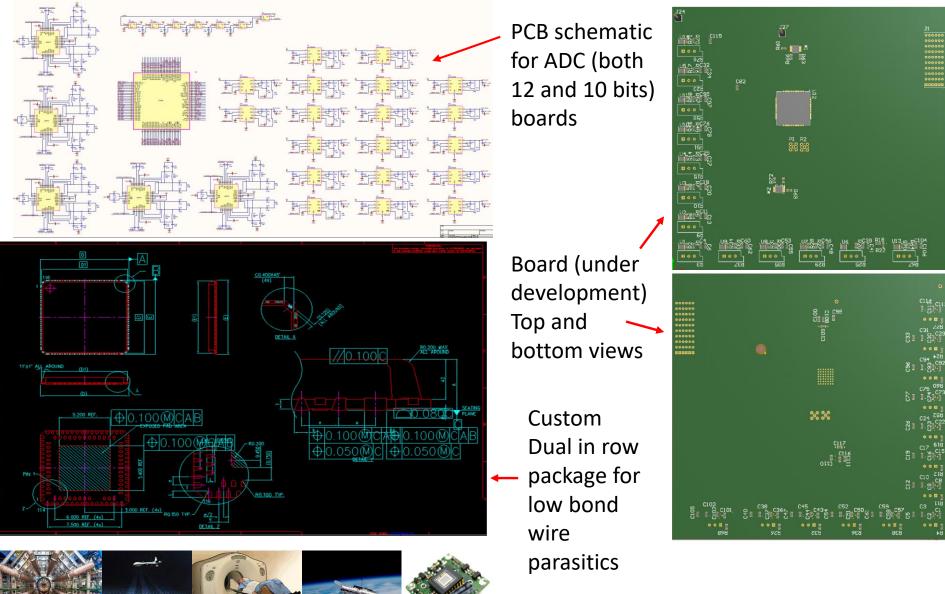

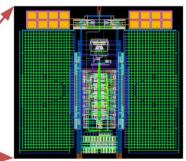

Figure 3: Alphacore's test chips sent for fabrication to measure performance of 12bit 100MS/s ADC (left) and 10bit 50MS/s ADC (right) in different configurations (including time-interleaving). A total of three different layouts are sent for fabrication to test various configurations of the ADCs.

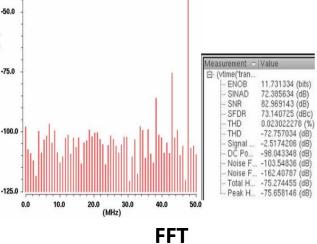

Figure 4: FFT response of 12bit, 100MS/s and 10bit, 50MS/s ADCs

# **RADHARD JESD204A Serialized I/O**

Robust High Performance Microelectronics

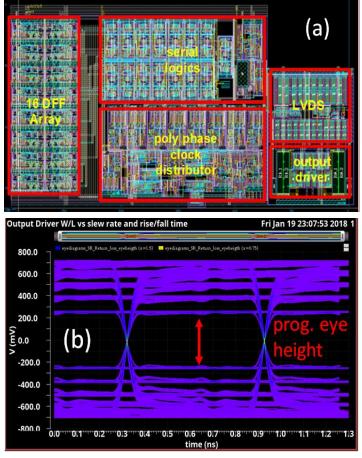

Provides robust 800Mb/s, or 1.6Gb/s speeds per single I/O pair

Figure 6: a) Alphacore's serializer layout and b) programmable eye height for easy signal swing matching to FPGA receiver.

Figure 7: 400MHz – 800MHz PLL layout

#### Preparation for Chip Evaluations, Status (1/2)

TEST\_OUT

For testing the

output of sub

. blocks

Output of

circuit

ch 1 ( ) (ch 2 LVDS Equalizer LVDS LINK MAX9218 MAX9247 Cable JP17 0 back side) REE PCL

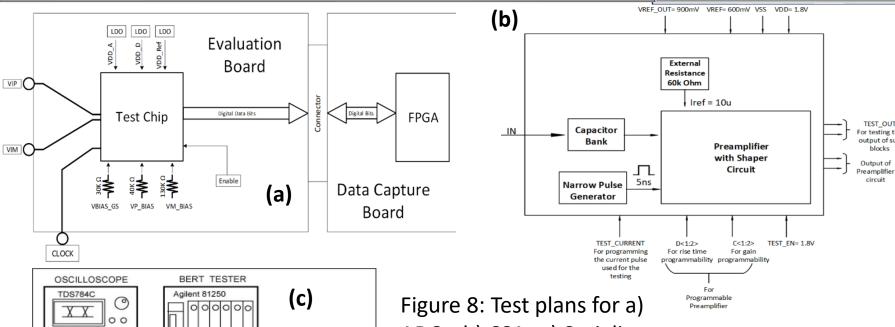

ADCs, b) CSAs c) Serializer

Wide functionality testing will be performed with lab equipment and COTS ADC evaluation boards.

© 2018

#### Preparation for Chip Evaluations, Status (2/2)

Robust High Performance Microelectronics

### New Development: 12b, 50MSPS, 9mW ADC for Cryogenic Operation

0.0

-25.0

(gp)

Robust High Performance Microelectronics

This rad-hard ADC is designed with 77K (cryogenic operation) transistor models. Available in ON Semiconductor 180nm CMOS process. Chips will arrive in December 2018.

#### Picosecond Timing Measurement IC for Particle Physics Experiments

<u>Requirement</u>: IC for accurate timing measurements and transient digitization 1 - 10 GSPS, timing resolution <1ps, conversion resolution > 9 ENOB, and power < 1W.

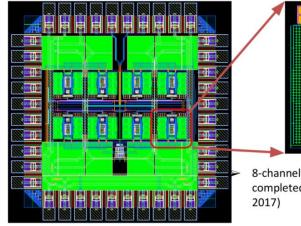

8-channel 10-bit 2-3 GS/s SAR ADC layout completed (tapeout scheduled for November 2017)

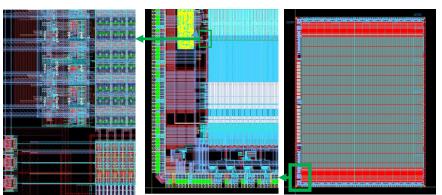

Layout of Alphacore's highspeed, high-resolution SAR ADC

#### Status: Chips will arrive for testing this week !

**DOE SBIR Phase II**

Key Features:

- Innovative successive approximation register

(SAR) analog-to-digital converter (ADC)

- Fully continuous ADC with no sample buffer depth or dead-time limitation.

- Jitter and time-skew both < 100fs

| Specification                             | Alphacore's ADC                                                      |  |

|-------------------------------------------|----------------------------------------------------------------------|--|

| Sampling Speed (GSPS)                     | 1 - 10                                                               |  |

| Analog Bandwidth, 3dB (GHz)               | >5                                                                   |  |

| Resolution                                | 10                                                                   |  |

| ENOB                                      | 8.5 (at 10GSPS and 5GHz)                                             |  |

| Unit ADCs per chip                        | 4 x 8                                                                |  |

| Aperture Jitter, random (RMS)             | 80fs                                                                 |  |

| ENOB (at 1GHz, random jitter<br>included) | >8.6                                                                 |  |

| Radiation hardness                        | >300 krad                                                            |  |

| Power (per channel) (mW)                  | <200 (at f <sub>s</sub> = 10GSPS)<br><70 (at f <sub>s</sub> = 3GSPS) |  |

| Buffer depth (points per sample)          | Unlimited                                                            |  |

| Latency (ns)                              | 3                                                                    |  |

| Interface type and total output rate      | 8b/10b encoded, serialized CML, 125Gb/s                              |  |

| CMOS node                                 | 28nm                                                                 |  |

#### **Fully Continuous Real-Time ADC vs. Switched Capacitor Array Digitizer**

**Robust High** Performance **Microelectronics**

| Specification                          | Alphacore's<br>Continuous 180nm<br>CMOS ADC | Alphacore's 28nm CMOS Switched-<br>Capacitor Array Digitizer | Alphacore's<br>Continuous 28nm<br>CMOS ADC |

|----------------------------------------|---------------------------------------------|--------------------------------------------------------------|--------------------------------------------|

| Resolution (bits)                      | 10-12                                       | 10 - 12                                                      | 10                                         |

| Sampling rate                          | 100 MSPS                                    | 1 – 6 GSPS                                                   | 1-10 GSPS                                  |

| Input bandwidth                        | 100MHz                                      | >3GHz                                                        | >5GHz                                      |

| Channels per chip                      | 8                                           | 8                                                            | 4                                          |

| Power per channel                      | 70mW                                        | <10mW                                                        | 70mW                                       |

| Deadtime between inputs pulses         | 10ns                                        | 500ns                                                        | 3ns                                        |

| Maximum input pulse rate               | 50MHz                                       | 2MHz (up to 10MHz with higher power)                         | 1.5GHz                                     |

| Sampling buffer depth                  | Infinite                                    | 1,024                                                        | Infinite                                   |

| Time skew                              | 300fs                                       | <2ps                                                         | 80fs                                       |

| Jitter                                 | 300fs                                       | <2ps                                                         | 80fs                                       |

| Price per channel for 2,000 channels   | \$40                                        | ~\$100                                                       | <\$200                                     |

| Price per channel for 20,000 channels  | \$15-20                                     | ~\$30                                                        | ~\$50                                      |

| Price per channel for 100,000 channels | ~\$10                                       | ~\$25                                                        | <\$40                                      |

| Current status                         | Taped out                                   | Schematic-level design                                       | Taped out                                  |

Note that preamplifiers have comparable or lower per-channel pricing than the 180nm ADC. Questions: Is a GHz digitizer IC needed as well? Will pulse rate be >10MHz in any experiment? Is a switched capacitor array digitizer with 500ns deadtime a good match to the applications?

# **Rad-Hard High-Speed Camera**

<u>Requirement</u>: A triggerable, high speed imaging chip and a complete camera system for investigating rapidly occurring phenomena in radiation environments. The primary application is beam monitoring in accelerator facilities.

Key specs include:

- 1 Megapixel

- 20µm x 20µm pixel size

- 10,000 frames per second continuous video output

- 120Gb/s total output data rate

- Low-noise pinned photodiodes

- ADC ENOB = 10.3 bits

- The chip has 8,000 X 12b, 3MSPS ADCs

- 300krad(Si) radiation tolerance

Status 10,000pixel, 10,000FPS image sensor and camera tested and fond functional. 1Mpix, 10,000FPS version of the image sensor taped out in September 2018.

DOF SBIR

Phase I & Phase II

Zoom: Px array, column bias, row decoders, ...

Zoom: Pixels, column ADCs, PLL, ...

Full 1 Mpx chip 27mm x 22mm

# Summary

- Alphacore presented the current status of detector readout IC development including rad-hard preamplifiers, ADCs and combined ROICs.

- Large tapeout was completed and IC testing will start in January 2019.

- **Questions for the audience?**

- Is there a need for a "Combined ROIC", i.e. a chip that has both preamplifiers and ADCs, or can they be on separate chips?

- What are the target experiments, their schedule, channel counts, and readout specifications?

- Radiation hardness requirements?

- Integration level requirements (IP? Wafers? Packaged chips? Packaged and tested chips? Evaluation boards? Ready-made readout boards with FPGAs ?)

Esko Mikkola, CEO <u>www.alphacoreinc.com</u> Office +1 480-494-5816 Mobile +1 520-647-4445 <u>Esko.Mikkola@alphacoreinc.com</u>

Phaneendra "Phani" Bikkina, Principal Design Engineer <u>Phaneendra.Bikkina@alphacoreinc.com</u>

> Daniel Mazidi, Design Engineer Daniel.Mazidi@alphacoreinc.com